<packt>

$$a = b + 2$$

;

%a = add nsw i32 % b, 2

%a:gpr32sp = nsw ADDWri %b:gpr32common, 2, 0

add w0, w0, #2

[0x00,0x08,0x00,0x11]

· bhabhabhabaa

010010 101000 010100 010001

# LLVM Code Generation

A deep dive into compiler backend development

### **Quentin Colombet**

Foreword by Kristof Beyls, Senior Technical Director and Fellow, Arm

# **LLVM Code Generation**

A deep dive into compiler backend development

**Quentin Colombet**

#### **LLVM Code Generation**

Copyright © 2025 Packt Publishing

All rights reserved. No part of this book may be reproduced, stored in a retrieval system, or transmitted in any form or by any means, without the prior written permission of the publisher, except in the case of brief quotations embedded in critical articles or reviews.

Every effort has been made in the preparation of this book to ensure the accuracy of the information presented. However, the information contained in this book is sold without warranty, either express or implied. Neither the author, nor Packt Publishing or its dealers and distributors, will be held liable for any damages caused or alleged to have been caused directly or indirectly by this book.

Packt Publishing has endeavored to provide trademark information about all of the companies and products mentioned in this book by the appropriate use of capitals. However, Packt Publishing cannot guarantee the accuracy of this information.

Portfolio Director: Kunal Chaudhari Relationship Lead: Samriddhi Murarka Project Manager: Ashwin Dinesh Kharwa

Content Engineer: Sujata Tripathi Technical Editor: Rohit Singh Copy Editor: Safis Editing Indexer: Hemangini Bari

Production Designer: Vijay Kamble

Growth Lead: Vinishka Kalra

First published: May 2025 Production reference: 2080525

1 Toddetton Telefence. 2000020

Published by Packt Publishing Ltd. Grosvenor House 11 St Paul's Square

Birmingham

B3 1RB, UK.

ISBN 978-1-83763-778-2

www.packtpub.com

## **Foreword**

At first glance, it might seem like only a few people ever work on LLVM backends. After all, the number of backends in upstream LLVM is limited, and most of them are already stable and functioning well. So, why would they need significant changes?

In reality, LLVM has become the de facto standard for code generation—not just for CPUs but also for increasingly diverse compute engines such as GPUs and other accelerators. When a new CPU or accelerator needs code generation support, the default choice is often to adopt LLVM and implement a backend.

Furthermore, the existing upstream backends are under constant improvement. They're regularly updated to support new CPU instructions, refine and enhance optimizations, introduce additional security-hardening features, and much more.

Beyond development in industry and by enthusiasts, LLVM is also a top choice in academia for systems and compiler research. Many innovations in performance tuning, security, and other areas require modifying LLVM backends to enable experimentation.

These are just a few scenarios where someone might need to create or modify LLVM backends—and I'm sure there are many more. But even considering just these three, it's clear that thousands of developers need to do at least some LLVM backend development, and they need high-quality documentation to do it well.

While the LLVM project offers extensive documentation and tutorials, there continues to be a gap in documenting very clearly everything you need to know to become proficient in backend development.

Effectively working on LLVM backends often requires reverse engineering and internalizing their architecture. Historically, the most efficient way to learn has been to find an expert and engage in long, detailed conversations to piece everything together. Of course, not everyone has access to such experts. Even though the LLVM community makes a huge effort to share expert knowledge—through comprehensive documentation (https://llvm.org/docs/), hundreds of recorded talks and presentations (https://llvm.org/devmtg/), and programs such as office hours and online sync-ups (https://llvm.org/docs/GettingInvolved.html#office-hours)—the learning curve remains steep.

A few years ago, I had a conversation with Quentin at one of the LLVM Developers' Meetings about this very topic. I thought then (and still do!) that Quentin is one of the most knowledgeable LLVM backend engineers out there. I was thinking out loud, "Wouldn't it be amazing if all of your knowledge—especially about LLVM backend development—could be made easily available to the entire LLVM community? Just imagine how much easier and faster backend development would become if your insights were accessible in a book..."

I'm thrilled that our conversation helped inspire Quentin to write this fantastic book. It distills deep insights and practical knowledge into a single, well-organized resource—ideal for anyone starting or continuing their journey in LLVM backend development. I hope that everyone working on backends reads it, and that it fuels even more innovation and progress in the LLVM ecosystem.

Thank you, Quentin, for writing all this down!

Kristof Beyls

Senior Technical Director and Fellow, Arm

## **Contributors**

#### About the author

**Quentin Colombet** is a veteran LLVM contributor who focuses on the development of backends. He is the architect of the new instruction selection framework (GlobalISel) and code owner of the LLVM register allocators.

He has more than two decades of experience working on different compiler backends for various architectures (GPU, CPU, microcontroller, DSP, and ASIC, among others) and compiler frameworks (Open64, LLVM, IREE, and Glow, to name the main ones). He joined the LLVM project when he started at Apple in 2012 and has worked on the x86, AArch64, and Apple GPU backends and all the products that include these processing units. Since starting on the LLVM infrastructure, he has helped interns and new hires onboard the LLVM infrastructure at Apple, Meta, and Google, as well as, more recently, his own company, Brium, while contributing to the projects using that technology in these companies.

I want to thank Bruno Cardoso Lopes, who inspired me to write this book and introduced me to the Packt team. Thank you to the Packt team for their support and continuous feedback, more specifically, Aditi Chatterjee, Ashwin Dinesh Kharwa, Samriddhi Murarka, and Sujata Tripathi, who all worked closely with me to make this project a reality. Thanks to my technical reviewer, Shuo Niu, who brought a different perspective to the book and helped me clarify the content, resulting in a better experience. And, of course, thank you to my wife, Luce, who encouraged me to get started on this project and supported me along the way.

#### About the reviewer

**Shuo Niu** holds a Master of Engineering in computer engineering from the University of Toronto. With six years of experience in LLVM compiler development, specializing in middle-end and backend optimizations for FPGA HLS compilers, Shuo is now extending his expertise to building AI compilers for low-power AI chips. Committed to fostering a stronger LLVM community, Shuo also served as a technical reviewer for *Learn LLVM 17, Second Edition*.

# **Table of Contents**

| Pretace                                                            | XXV |

|--------------------------------------------------------------------|-----|

| Part 1: Getting Started with LLVM                                  | 1   |

| Chapter 1: Building LLVM and Understanding the Directory Structure | 3   |

| Technical requirements                                             | 4   |

| Getting ready for LLVM's world                                     | 4   |

| Prerequisites • 5                                                  |     |

| Identifying the right version of the tools • 6                     |     |

| Installing the right tools • 7                                     |     |

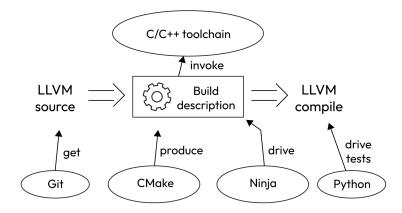

| Building a compiler                                                | 8   |

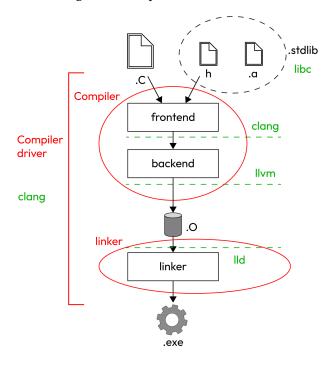

| What is a compiler? • 9                                            |     |

| Opening Clang's hood • 9                                           |     |

| Building Clang • 11                                                |     |

| Experimenting with Clang • 11                                      |     |

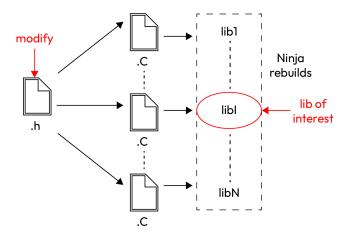

| Building LLVM                                                      | 12  |

| Configuring the build system • 13                                  |     |

| Crash course on Ninja • 16                                         |     |

| Building the core LLVM project • 18                                |     |

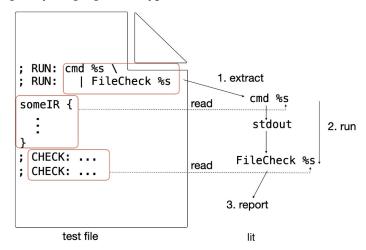

| Testing a compiler                                                 | 19  |

| Crash course on the Google test infrastructure • 19                |     |

| Crash course on the LLVM Integrated Tester • 19                    |     |

| Testing in lit • 20                                                |     |

| Directives • 20                                                    |     |

| Describing the RUN command • 21                                    |     |

| The lit driver – llvm-lit • 22                                     |     |

Table of Contents

| Crash course on FileCheck • 23                                              |      |

|-----------------------------------------------------------------------------|------|

| FileCheck by example • 24                                                   |      |

| LLVM unit tests • 26                                                        |      |

| Finding the source of a test • 27                                           |      |

| Running unit tests manually • 27                                            |      |

| The unit tests pass, what now? • 30                                         |      |

| LLVM functional tests • 30                                                  |      |

| The LLVM test suite • 31                                                    |      |

| The functional tests fail – what do you do? • 32                            |      |

| Understanding the directory structure                                       | . 34 |

| High-level directory structure • 34                                         |      |

| Focusing on the core LLVM project • 34                                      |      |

| A word on the include files • 35                                            |      |

| Private headers • 35                                                        |      |

| What is the deal with <project>/include/<project>? • 35</project></project> |      |

| What is include/ <project>-c? • 36</project>                                |      |

| Overview of some of the LLVM components • 36                                |      |

| Generic LLVM goodness • 36                                                  |      |

| Working with the LLVM IR • 36                                               |      |

| Generic backend infrastructure • 37                                         |      |

| Target-specific constructs • 37                                             |      |

| Summary                                                                     | . 37 |

| Quiz time                                                                   | . 38 |

|                                                                             |      |

| Chapter 2: Contributing to LLVM                                             | 43   |

| Reporting an issue                                                          | . 43 |

| Engaging with the community                                                 | . 45 |

| Reviewing patches • 46                                                      |      |

| Contributing patches                                                        | . 47 |

| Understanding patch contribution in a nutshell • 48                         |      |

| Following up with your contribution • 49                                    |      |

| A word on adding tests • 49                                                 |      |

| Summary                                                                     | . 50 |

| Quiz time                                                                   | . 50 |

Table of Contents xi

| Chapter 3: Compiler Basics and How They Map to LLVM APIs 53 |

|-------------------------------------------------------------|

| Technical requirements                                      |

| A word on APIs                                              |

| Understanding compiler jargon 5                             |

| Target • 56                                                 |

| Host • 56                                                   |

| Lowering • 56                                               |

| Canonical form • 56                                         |

| Build time, compile time, and runtime • 56                  |

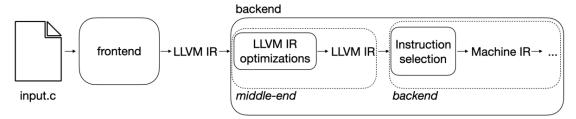

| Backend and middle-end • 57                                 |

| Application binary interface • 57                           |

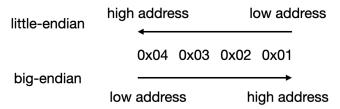

| Encoding • 58                                               |

| Working with basic structures 5                             |

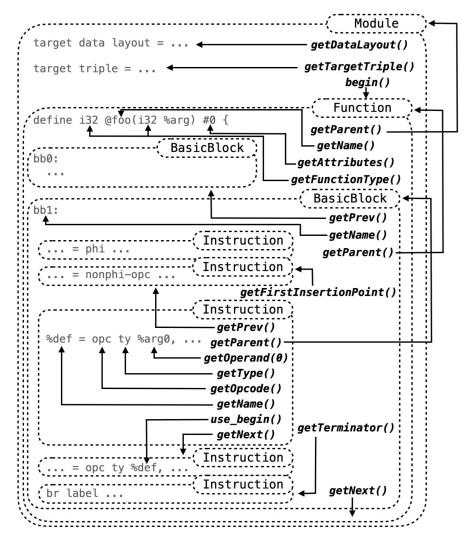

| Module • 59                                                 |

| A module at the LLVM IR level • 59                          |

| A module at the Machine IR level • 60                       |

| Function • 61                                               |

| A function in the LLVM IR • 62                              |

| A function in the Machine IR • 62                           |

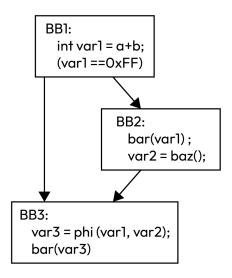

| Basic block • 63                                            |

| A basic block in the LLVM IR • 64                           |

| A basic block in the Machine IR • 65                        |

| Instruction • 66                                            |

| An instruction in the LLVM IR • 67                          |

| An instruction in the Machine IR • 67                       |

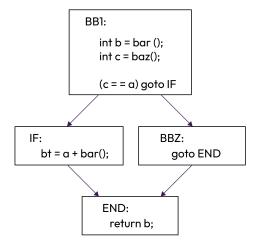

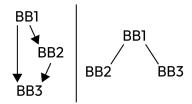

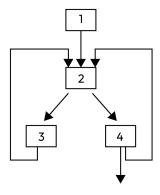

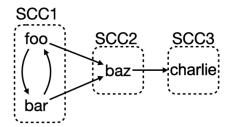

| Control flow graph • 68                                     |

| Reverse post-order traversal • 69                           |

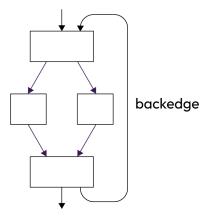

| Backedge • 70                                               |

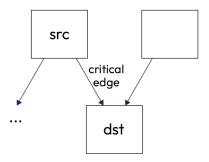

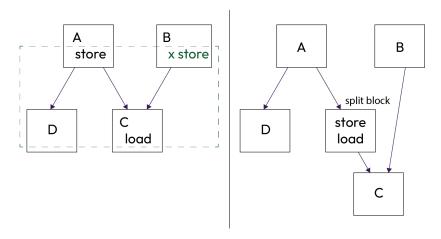

| Critical edge • 70                                          |

| Irreducible graph • 71                                      |

| Building your first IRs                                     |

| Building your first LLVM IR • 74                            |

| A walk over the required APIs • 74                          |

| Your turn • 75                                              |

xii Table of Contents

| Building your first Machine IR • 76                                                      |

|------------------------------------------------------------------------------------------|

| A walk over the required APIs • 76                                                       |

| Your turn • 78                                                                           |

| Summary                                                                                  |

| Quiz time                                                                                |

| Chapter 4: Writing Your First Optimization 83                                            |

| Technical requirements                                                                   |

| The concept of value                                                                     |

| SSA • 85                                                                                 |

| Constructing the SSA form • 86                                                           |

| Dominance • 88                                                                           |

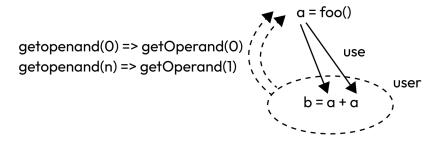

| Def-use and use-def chains • 91                                                          |

| Def-use and use-def chains in the LLVM IR • 91                                           |

| Def-use and use-def chains in the Machine IR • 94                                        |

| Tackling optimizations                                                                   |

| Legality • 96                                                                            |

| Integer overflow/underflow • 97                                                          |

| Fast-math flags • 97                                                                     |

| Side effects • 98                                                                        |

| Profitability • 99                                                                       |

| Instruction lowering – TargetTransformInfo and TargetLowering • 101                      |

| Library support – TargetLibraryInfo • 102                                                |

| Datatype properties – DataLayout • 102                                                   |

| Register pressure • 102                                                                  |

| Basic block frequency • 103                                                              |

| More precise instruction properties – scheduling model and instruction description • 104 |

| Transformation jargon • 104                                                              |

| Instcombine • 104                                                                        |

| Fixed point • 105                                                                        |

| Liveness • 105                                                                           |

| Hoisting • 105                                                                           |

| Sinking • 105                                                                            |

| Folding • 105                                                                            |

Table of Contents xiii

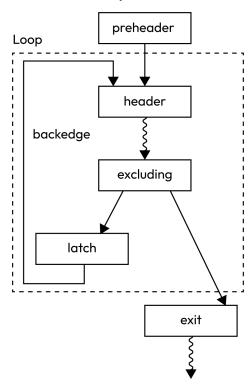

| Loops                                              | 106 |

|----------------------------------------------------|-----|

| Terminology • 106                                  | 100 |

| Preheader • 106                                    |     |

| Header • 107                                       |     |

| Exiting block • 107                                |     |

| Latch • 107                                        |     |

| Exit block • 107                                   |     |

|                                                    |     |

| Where to get loop information • 107                | 107 |

| Writing a simple constant propagation optimization | 107 |

| The optimization • 108                             |     |

| Simplifying assumptions • 108                      |     |

| Missing APIs • 108                                 |     |

| The Constant class • 108                           |     |

| The APInt class • 109                              |     |

| Creating a constant • 109                          |     |

| Replacing a value • 110                            |     |

| Your turn • 110                                    |     |

| Going further • 110                                |     |

| Legality • 110                                     |     |

| Profitability • 111                                |     |

| Propagating constants across types • 111           |     |

| Summary                                            | 112 |

| Quiz time                                          | 112 |

|                                                    |     |

| Chapter 5: Dealing with Pass Managers              | 115 |

| Technical requirements                             | 115 |

| What is a pass?                                    |     |

| What is a pass manager?                            |     |

| The legacy and new pass manager                    |     |

| Pass managers' capabilities • 118                  |     |

| Populating a pass manager • 119                    |     |

| Inner workings of pass managers • 120              |     |

| Creating a pass                                    | 121 |

| Writing a pass for the legacy pass manager • 121   | 161 |

| Using the proper base class • 121                  |     |

| Expressing the dependencies of a pass • 123        |     |

| Expressing the dependencies of a pass • 125        |     |

xiv Table of Contents

| Preserving analyses • 126                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |        |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| Specificities of the Pass class • 127                                                                                                                                                                                                                                                                                                                                                                                                                                                     |        |

| Writing a pass for the new pass manager • 128                                                                                                                                                                                                                                                                                                                                                                                                                                             |        |

| Implementing the right method • 128                                                                                                                                                                                                                                                                                                                                                                                                                                                       |        |

| Registering an analysis • 129                                                                                                                                                                                                                                                                                                                                                                                                                                                             |        |

| Describing the effects of your pass • 130                                                                                                                                                                                                                                                                                                                                                                                                                                                 |        |

| Inspecting the pass pipeline                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 131    |

| Available developer tools • 131                                                                                                                                                                                                                                                                                                                                                                                                                                                           |        |

| Plumbing up the information you need • 132                                                                                                                                                                                                                                                                                                                                                                                                                                                |        |

| Interpreting the logs of pass managers • 134                                                                                                                                                                                                                                                                                                                                                                                                                                              |        |

| The pass pipeline structure • 134                                                                                                                                                                                                                                                                                                                                                                                                                                                         |        |

| Time profile • 137                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |        |

| Your turn                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 138    |

| Writing your own pass • 138                                                                                                                                                                                                                                                                                                                                                                                                                                                               |        |

| Writing your own pass pipeline • 139                                                                                                                                                                                                                                                                                                                                                                                                                                                      |        |

| Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |        |

| Further reading                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 140    |

| Further reading                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |        |

| Quiz time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 141    |

| Quiz time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ng 143 |

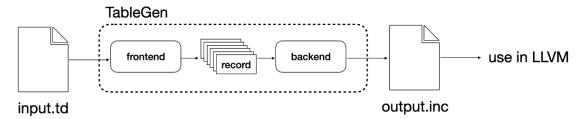

| Quiz time  Chapter 6: TableGen — LLVM Swiss Army Knife for Modelin  Technical requirements                                                                                                                                                                                                                                                                                                                                                                                                | ng 143 |

| Quiz time  Chapter 6: TableGen — LLVM Swiss Army Knife for Modelin  Technical requirements  Getting started with TableGen                                                                                                                                                                                                                                                                                                                                                                 |        |

| Quiz time  Chapter 6: TableGen — LLVM Swiss Army Knife for Modelin  Technical requirements  Getting started with TableGen  The TableGen programming language                                                                                                                                                                                                                                                                                                                              |        |

| Quiz time  Chapter 6: TableGen — LLVM Swiss Army Knife for Modelin  Technical requirements  Getting started with TableGen  The TableGen programming language  Types • 147                                                                                                                                                                                                                                                                                                                 |        |

| Quiz time  Chapter 6: TableGen — LLVM Swiss Army Knife for Modelin  Technical requirements  Getting started with TableGen  The TableGen programming language  Types • 147  Programming with TableGen • 148                                                                                                                                                                                                                                                                                |        |

| Quiz time  Chapter 6: TableGen — LLVM Swiss Army Knife for Modelin  Technical requirements  Getting started with TableGen  The TableGen programming language  Types • 147  Programming with TableGen • 148  Defining multiple records at once • 149                                                                                                                                                                                                                                       |        |

| Quiz time  Chapter 6: TableGen — LLVM Swiss Army Knife for Modelin  Technical requirements  Getting started with TableGen  The TableGen programming language  Types • 147  Programming with TableGen • 148                                                                                                                                                                                                                                                                                |        |

| Quiz time  Chapter 6: TableGen — LLVM Swiss Army Knife for Modelin  Technical requirements  Getting started with TableGen  The TableGen programming language  Types • 147  Programming with TableGen • 148  Defining multiple records at once • 149                                                                                                                                                                                                                                       |        |

| Quiz time  Chapter 6: TableGen — LLVM Swiss Army Knife for Modelin  Technical requirements  Getting started with TableGen  The TableGen programming language  Types • 147  Programming with TableGen • 148  Defining multiple records at once • 149  Assigning fields • 151                                                                                                                                                                                                               |        |

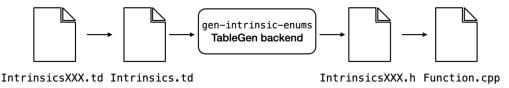

| Quiz time  Chapter 6: TableGen — LLVM Swiss Army Knife for Modelin  Technical requirements  Getting started with TableGen  The TableGen programming language  Types • 147  Programming with TableGen • 148  Defining multiple records at once • 149  Assigning fields • 151  Discovering a TableGen backend                                                                                                                                                                               |        |

| Quiz time  Chapter 6: TableGen — LLVM Swiss Army Knife for Modelin  Technical requirements  Getting started with TableGen  The TableGen programming language  Types • 147  Programming with TableGen • 148  Defining multiple records at once • 149  Assigning fields • 151  Discovering a TableGen backend  General information on TableGen backends for LLVM • 153                                                                                                                      |        |

| Quiz time  Chapter 6: TableGen — LLVM Swiss Army Knife for Modeling Technical requirements Getting started with TableGen  The TableGen programming language  Types • 147 Programming with TableGen • 148 Defining multiple records at once • 149 Assigning fields • 151  Discovering a TableGen backend  General information on TableGen backends for LLVM • 153 Discovering a TableGen backend • 155                                                                                     |        |

| Quiz time  Chapter 6: TableGen — LLVM Swiss Army Knife for Modeling  Technical requirements  Getting started with TableGen  The TableGen programming language  Types • 147  Programming with TableGen • 148  Defining multiple records at once • 149  Assigning fields • 151  Discovering a TableGen backend  General information on TableGen backends for LLVM • 153  Discovering a TableGen backend • 155  The implementation of intrinsics • 155                                       |        |

| Quiz time  Chapter 6: TableGen — LLVM Swiss Army Knife for Modeling Technical requirements  Getting started with TableGen  The TableGen programming language  Types • 147  Programming with TableGen • 148  Defining multiple records at once • 149  Assigning fields • 151  Discovering a TableGen backend  General information on TableGen backends for LLVM • 153  Discovering a TableGen backend • 155  The implementation of intrinsics • 155  The content of a generated file • 155 |        |

| Chapter 6: TableGen — LLVM Swiss Army Knife for Modeling Technical requirements                                                                                                                                                                                                                                                                                                                                                                                                           |        |

Table of Contents xv

| Summary                                | . 160 |

|----------------------------------------|-------|

| Further reading                        | 160   |

| Quiz time                              | . 161 |

|                                        |       |

| Part 2: Middle-End: LLVM IR to LLVM IR | 163   |

| Chapter 7: Understanding LLVM IR       | 165   |

| Technical requirements                 | 166   |

| Understanding the need for an IR       | 166   |

| What an IR is • 166                    |       |

| Why use an IR? • 166                   |       |

| Introducing LLVM IR                    | 167   |

| Identifiers • 167                      |       |

| Functions • 168                        |       |

| Basic blocks • 170                     |       |

| Instructions • 171                     |       |

| Types • 172                            |       |

| Single-value types • 172               |       |

| The label type • 175                   |       |

| Aggregate types • 176                  |       |

| Types in the LLVM IR API • 178         |       |

| Walking through an example             | 179   |

| Target-specific elements in LLVM IR    | 182   |

| Intrinsic functions • 182              |       |

| Triple • 184                           |       |

| Function attributes • 184              |       |

| Data layout • 185                      |       |

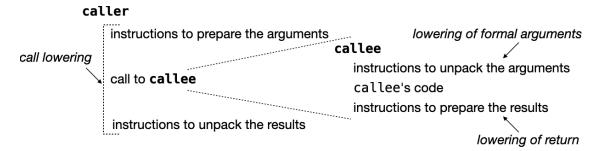

| Application binary interface • 189     |       |

| Textual versus binary format           | . 191 |

| LLVM IR API – cheat sheet              | 192   |

| Summary                                | 194   |

| Further reading                        | 194   |

| Quiz time                              | 195   |

xvi Table of Contents

| Chapter 8: Survey of the Existing Passes          | 197 |

|---------------------------------------------------|-----|

| Technical requirements                            | 198 |

| How to find the unknown                           | 198 |

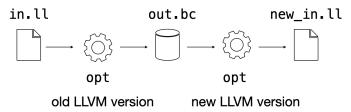

| Leveraging opt • 198                              |     |

| Using the LLVM code base • 201                    |     |

| Starting from the implementation • 202            |     |

| Survey of the helper passes                       | 203 |

| The verifier • 203                                |     |

| The printer • 204                                 |     |

| Analysis passes • 206                             |     |

| Target transformation information • 206           |     |

| Loop information • 207                            |     |

| Alias analysis • 207                              |     |

| Block frequency info • 208                        |     |

| Dominator tree information • 208                  |     |

| Value tracking • 209                              |     |

| Canonicalization passes                           | 209 |

| The instruction combiner • 211                    |     |

| An example of a canonical rewrite • 211           |     |

| An example of an optimization • 212               |     |

| How to use instcombine • 212                      |     |

| The memory to register rewriter • 213             |     |

| The converter to loop-closed-SSA form • 213       |     |

| Optimization passes                               | 216 |

| Interprocedural optimizations • 217               |     |

| Scalar optimizations • 220                        |     |

| Vectorization • 229                               |     |

| Summary                                           | 232 |

| Further reading                                   | 232 |

| Quiz time                                         | 233 |

| Chapter 9: Introducing Target-Specific Constructs | 235 |

| Technical requirements                            | 236 |

| Adding a new backend in LLVM                      | 237 |

| Connecting your target to the build system • 237  |     |

| Registering your target with Clang • 241          |     |

Table of Contents xvii

| Adding a new architecture to the Triple class • 242                 |     |

|---------------------------------------------------------------------|-----|

| Populating the Target instance • 243                                |     |

| Plumbing your Target through Clang • 247                            |     |

| Creating your own intrinsics                                        | 252 |

| The pros and cons of intrinsics • 252                               |     |

| Creating an intrinsic in the backend • 254                          |     |

| Defining our intrinsics • 255                                       |     |

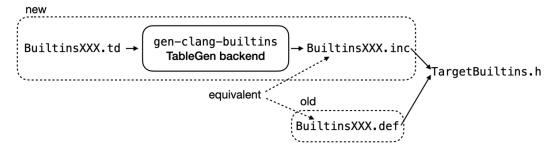

| Hooking up the TableGen backend • 257                               |     |

| Teaching LLVM IR about our intrinsics • 258                         |     |

| Connecting an intrinsic to Clang • 258                              |     |

| Writing the .def file by hand • 259                                 |     |

| Using the TableGen capabilities • 261                               |     |

| Hooking up the built-in information • 262                           |     |

| Establishing the code generation link • 263                         |     |

| Adding a target-specific TargetTransformInfo implementation         | 265 |

| Establishing a connection to your target-specific information • 265 |     |

| Introducing target-specific costs • 266                             |     |

| Customizing the default middle-end pipeline                         | 268 |

| Using the new pass manager • 268                                    |     |

| Using the legacy pass manager • 270                                 |     |

| A one-time setup – assembling a codegen pipeline • 271              |     |

| Faking the instruction selector • 272                               |     |

| Faking the lowering of the object file • 273                        |     |

| Creating a skeleton for the assembly information • 274              |     |

| Using the right abstraction                                         | 277 |

| Summary                                                             | 278 |

| Further reading                                                     | 278 |

| Quiz time                                                           | 279 |

| Chapter 10: Hands-On Debugging LLVM IR Passes                       | 281 |

| Technical requirements                                              | 281 |

| The logging capabilities in LLVM                                    | 282 |

| Printing the IR between passes • 282                                |     |

| Printing the debug log • 283                                        |     |

| Printing high-level information about what happened • 285           |     |

|                                                                     |     |

xviii Table of Contents

| Reducing the input IR size                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 287 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Extracting a subset of the input IR • 287                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |

| Shrinking the IR automatically • 289                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |

| Using sanitizers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 291 |

| A crash course on LLDB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |

| Starting a debugging session • 293                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |     |

| Controlling the execution • 294                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |     |

| Stopping the program • 295                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     |

| Command resolution • 296                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |

| Resuming the execution • 297                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |

| Inspecting the state of a program • 299                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |

| The LLVM code base through a debugger                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 301 |

| Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 303 |

| Further reading                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |     |

| Quiz time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 304 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 307 |

| Part 3: Introduction to the Backend                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |

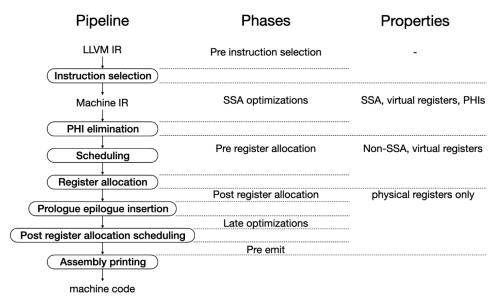

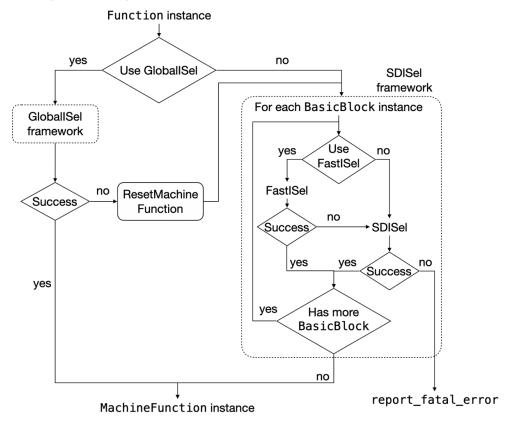

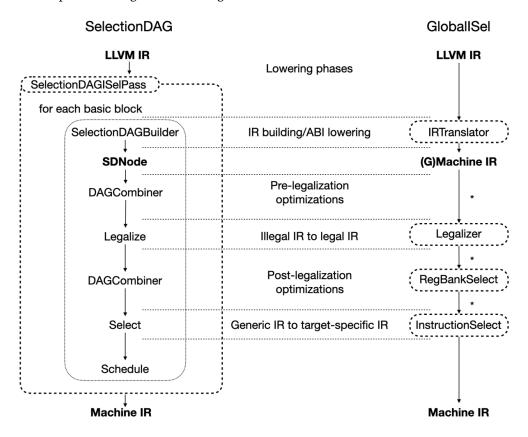

| Part 3: Introduction to the Backend  Chapter 11: Getting Started with the Backend                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 309 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |     |

| Chapter 11: Getting Started with the Backend  Technical requirements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 309 |

| Chapter 11: Getting Started with the Backend  Technical requirements  Introducing the Machine IR                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

| Chapter 11: Getting Started with the Backend  Technical requirements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |

| Chapter 11: Getting Started with the Backend  Technical requirements  Introducing the Machine IR  Here comes the Machine IR                                                                                                                                                                                                                                                                                                                                                                                                                                     |     |

| Chapter 11: Getting Started with the Backend  Technical requirements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |

| Chapter 11: Getting Started with the Backend  Technical requirements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |

| Chapter 11: Getting Started with the Backend  Technical requirements  Introducing the Machine IR  Here comes the Machine IR  The Machine IR textual representation  The .mir file format • 311  A primer on the YAML syntax • 312  The semantics of the different fields • 314                                                                                                                                                                                                                                                                                  |     |

| Chapter 11: Getting Started with the Backend  Technical requirements  Introducing the Machine IR  Here comes the Machine IR  The Machine IR textual representation  The .mir file format • 311  A primer on the YAML syntax • 312  The semantics of the different fields • 314  Mapping the content of a .mir file to the C++ API • 314                                                                                                                                                                                                                         |     |

| Chapter 11: Getting Started with the Backend  Technical requirements  Introducing the Machine IR  Here comes the Machine IR  The Machine IR textual representation  The .mir file format • 311  A primer on the YAML syntax • 312  The semantics of the different fields • 314                                                                                                                                                                                                                                                                                  |     |

| Chapter 11: Getting Started with the Backend  Technical requirements  Introducing the Machine IR  Here comes the Machine IR  The Machine IR textual representation  The .mir file format • 311  A primer on the YAML syntax • 312  The semantics of the different fields • 314  Mapping the content of a .mir file to the C++ API • 314  A deep dive into the body of a MachineFunction instance • 315                                                                                                                                                          |     |

| Chapter 11: Getting Started with the Backend  Technical requirements  Introducing the Machine IR  Here comes the Machine IR  The Machine IR textual representation  The .mir file format • 311  A primer on the YAML syntax • 312  The semantics of the different fields • 314  Mapping the content of a .mir file to the C++ API • 314  A deep dive into the body of a MachineFunction instance • 315  Working with a .mir file • 318                                                                                                                          |     |

| Chapter 11: Getting Started with the Backend  Technical requirements  Introducing the Machine IR  Here comes the Machine IR  The Machine IR textual representation  The .mir file format • 311  A primer on the YAML syntax • 312  The semantics of the different fields • 314  Mapping the content of a .mir file to the C++ API • 314  A deep dive into the body of a MachineFunction instance • 315  Working with a .mir file • 318  Generating a .mir file • 318                                                                                            |     |

| Chapter 11: Getting Started with the Backend  Technical requirements  Introducing the Machine IR  Here comes the Machine IR  The Machine IR textual representation  The .mir file format • 311  A primer on the YAML syntax • 312  The semantics of the different fields • 314  Mapping the content of a .mir file to the C++ API • 314  A deep dive into the body of a MachineFunction instance • 315  Working with a .mir file • 318  Generating a .mir file • 318  Running passes • 319                                                                      |     |

| Chapter 11: Getting Started with the Backend  Technical requirements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |

| Chapter 11: Getting Started with the Backend  Technical requirements  Introducing the Machine IR  Here comes the Machine IR  The Machine IR textual representation  The .mir file format • 311  A primer on the YAML syntax • 312  The semantics of the different fields • 314  Mapping the content of a .mir file to the C++ API • 314  A deep dive into the body of a MachineFunction instance • 315  Working with a .mir file • 318  Generating a .mir file • 318  Running passes • 319  Shrinking a .mir file • 321  The anatomy of a MachineInstr instance |     |

Table of Contents xix

| Dealing with explicit and implicit operands • 327                                                                                                                                                                                                                                                                                                                                                                                                |                          |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

| Understanding the constraints of an operand • 328                                                                                                                                                                                                                                                                                                                                                                                                |                          |

| Working with registers                                                                                                                                                                                                                                                                                                                                                                                                                           | 329                      |

| The concept of the register class • 331                                                                                                                                                                                                                                                                                                                                                                                                          |                          |

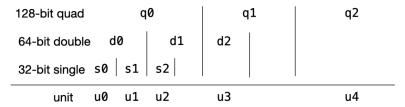

| The concept of sub-registers • 331                                                                                                                                                                                                                                                                                                                                                                                                               |                          |

| The concept of register tuples • 332                                                                                                                                                                                                                                                                                                                                                                                                             |                          |

| The concept of register units • 333                                                                                                                                                                                                                                                                                                                                                                                                              |                          |

| The registers and SSA and non-SSA forms • 335                                                                                                                                                                                                                                                                                                                                                                                                    |                          |

| Interacting with registers in the debugger • 336                                                                                                                                                                                                                                                                                                                                                                                                 |                          |

| Creating MachineInstr objects                                                                                                                                                                                                                                                                                                                                                                                                                    | 338                      |

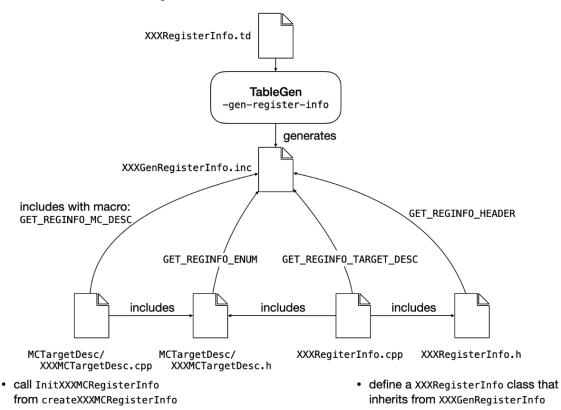

| Describing registers                                                                                                                                                                                                                                                                                                                                                                                                                             | 340                      |

| Writing the target description • 340                                                                                                                                                                                                                                                                                                                                                                                                             |                          |

| Describing instructions                                                                                                                                                                                                                                                                                                                                                                                                                          | 346                      |

| Summary                                                                                                                                                                                                                                                                                                                                                                                                                                          | 349                      |

| Further reading                                                                                                                                                                                                                                                                                                                                                                                                                                  | 349                      |

| Quiz time                                                                                                                                                                                                                                                                                                                                                                                                                                        | 349                      |

| Chapter 12: Getting Started with the Machine Code Layer                                                                                                                                                                                                                                                                                                                                                                                          | 353                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                          |

| Technical requirements                                                                                                                                                                                                                                                                                                                                                                                                                           |                          |

| Technical requirements                                                                                                                                                                                                                                                                                                                                                                                                                           | 354                      |

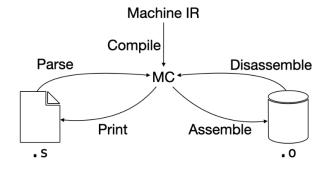

| The use of the MC layer                                                                                                                                                                                                                                                                                                                                                                                                                          | 354<br>354               |

| The use of the MC layer                                                                                                                                                                                                                                                                                                                                                                                                                          | 354<br>354               |

| The use of the MC layer  Connecting the MC layer  What instructions to describe • 356                                                                                                                                                                                                                                                                                                                                                            | 354<br>354               |

| The use of the MC layer  Connecting the MC layer                                                                                                                                                                                                                                                                                                                                                                                                 | 354<br>354               |

| The use of the MC layer                                                                                                                                                                                                                                                                                                                                                                                                                          | 354<br>354               |

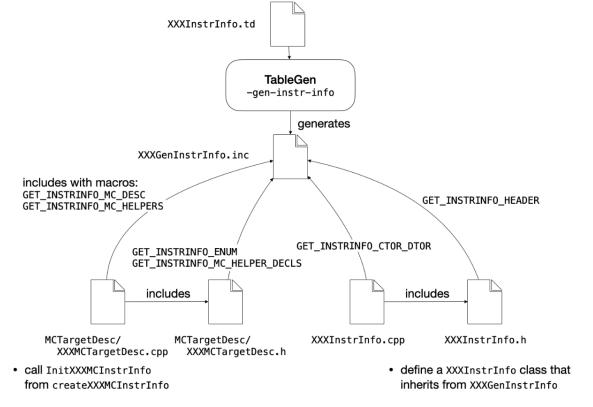

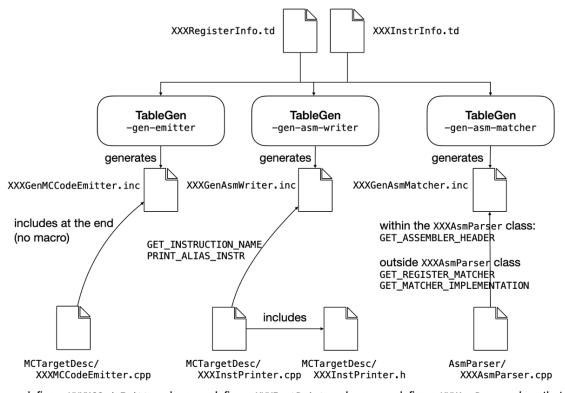

| The use of the MC layer  Connecting the MC layer  What instructions to describe • 356  Augmenting the target description with MC information • 356  Defining the MC layer for the registers • 357  Defining the MC layer for the instructions • 357                                                                                                                                                                                              | 354<br>354<br>355        |

| The use of the MC layer  Connecting the MC layer  What instructions to describe • 356  Augmenting the target description with MC information • 356  Defining the MC layer for the registers • 357  Defining the MC layer for the instructions • 357  Enabling MC-based tools                                                                                                                                                                     | 354<br>354<br>355        |