# Inside the

The AS/400's chief architect provides an in-depth look at the system's design, architecture, and history

BY FRANK G. SOLTIS

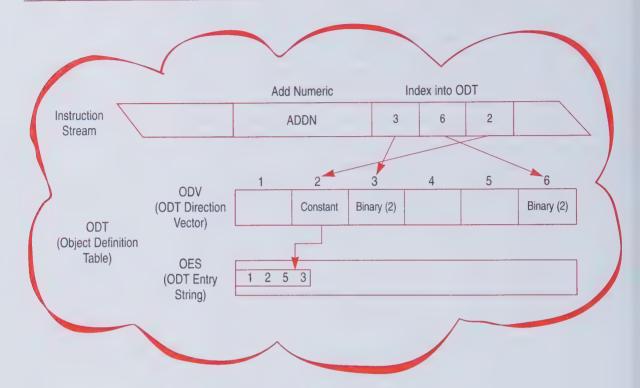

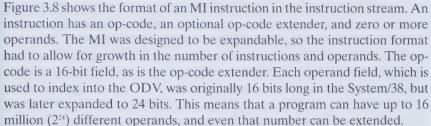

# Here's the Inside Story Every AS/400 Developer Has Been Waiting For

Told by Dr. Frank G. Soltis, IBM's AS/400 chief architect, this authoritative book looks at the AS/400's design, architecture, history — and at some of the people behind the scenes who created this revolutionary system for you.

Whether you are an executive looking for a high-level overview or a "bit-twiddling techie" who wants all the details, Inside the AS/400 demystifies this system, shedding light on how it came to be, how it can do the things it does, and what its future may hold — especially in light of its new PowerPC RISC processors.

### ALSO INCLUDED ARE DETAILED LOOKS AT THE $AS/400^{\circ}$ S

- advanced application architecture

- technology-independent machine interface

- ' objects and object management

- integrated database

- ' security and authorization

- single-level store

- ' process management

- 1/O system

- · client/server computing

Simply, Inside the AS/400 is written for those who want to learn more about the AS/400 from someone who knows. It is written for you, the customer and application developer, who want to understand how the AS/400 works so you can write better applications, or simply so you can see what makes this system tick.

Is the AS/400 magic, or just good design? After reading Inside the AS/400, perhaps you will agree that it's a little of both.

Stew Lelie

# Inside the AS/400

BY FRANK G. SOLTIS

A Division of **DUKE COMMUNICATIONS** INTERNATIONAL

Loveland, Colorado

#### Library of Congress Cataloging-in-Publication Data

Soltis, Frank, 1940-

Inside the AS/400: an in-depth look at the AS/400's design, architecture, and history / by Frank Soltis.

p. cm.

Includes index.

ISBN 1-882419-13-8

1. IBM AS/400 (Computer) I. Title.

QA76.8.125919S64 1995

004.2'545—dc20

95-33232 CIP

Copyright © 1996 by DUKE PRESS **DUKE COMMUNICATIONS** INTERNATIONAL Loveland, Colorado

All rights reserved. No part of this book may be reproduced in any form by any electronic or mechanical means (including photocopying, recording, or information storage and retrieval) without permission in writing from the publisher.

It is the reader's responsibility to ensure procedures and techniques used from this book are accurate and appropriate for the user's installation. No warranty is implied or expressed.

This book was printed and bound in the United States of America.

ISBN 1-882419-13-8

2 3 4 5 KP 9 8 7 6 5

To the love of my life for more than 31 years, my wife, Sandra.

# **Acknowledgments**

As long as 10 years ago, I considered writing this book. Those were the System/38 days, and people such as Paul Conte were encouraging me to write a book about the System/38 and the people who created it. But it was 1985, and the System/38 had been declared a "non-strategic" product within IBM. It was not obvious this system had any future. With the rebirth of the System/38 as the AS/400 in 1988, I began to write a book about the history, the people, and the development of these two systems. Over the past seven years, I have continued to plug away at that manuscript. Paul and others have encouraged me to finish that history book and share the Rochester story with the rest of the world. *Inside the AS/400* does contain a few historical excerpts from that unpublished manuscript.

Rochester is the most creative site in all of IBM. In the last few years, IBM has received lots of criticism for its inability to capitalize on its own technologies and to recognize the emerging needs of its customers. Yet, year after year, the dedicated men and women in Rochester continue to turn out creative, successful products that delight our customers and bring financial rewards to IBM. Rochester has never been very good at winning the "battle of the foil projectors" at IBM headquarters, but we have always been very good at winning the battle for customers.

Throughout this book, I have tried to name some of those creative, dedicated people who are responsible for the success of the AS/400. It is an impossible task, and I have only been able to name a few. For all of you who are not named, please accept my apologies. Even after 32 years of working for IBM in Rochester, hardly a day goes by that I don't feel inspired by the people around me. Thanks to all of you.

Mike Tomashek managed the development organization in Rochester that rewrote the internals of the AS/400 operating system for the PowerPC processors. It was clear in October 1991 that a massive education effort would be needed for the hundreds of new developers we were going to hire to write the new code. I had just spent the previous six months leading the effort to convince the management and technical leadership in Rochester to adopt the PowerPC technology for the AS/400. Now the project had been funded by IBM, and we were authorized to go out and hire

our first 200 people. Mike asked me to organize the education effort (in addition to my role in IBM, I am an adjunct professor and a member of the graduate faculty at the University of Minnesota). His request seemed reasonable, so I agreed.

As part of this education, I developed and taught the first classes on the internals of the AS/400. This undertaking would not have been possible without Jan Schliem working with me. Jan took on the responsibility to organize and manage the entire education project. That freed me to develop the class, and that class material formed the basis for this book. It was also Mike Tomashek who convinced me to turn this material into a book.

I also want to thank the Rochester people who reviewed the various chapters of this book and provided feedback for me. I especially want to thank two of them, Bruce Jawer and Larry Walsh, for being true believers in the AS/400 and for encouraging me to finish this project.

Working with the people at Duke Communications over the past few years has been an enjoyable experience for me. I had my first article published in NEWS 3X/400 (now NEWS/400) magazine in 1992, and I have managed to write something for that magazine every year since then. I have also enjoyed participating in the magazine's annual International Conference in Vail, Colorado, for the past three years. Dave Duke and his staff have done a marvelous job with the magazine and the conference. When it came time to select a publisher for this book, Duke Press was a natural choice. Dave Bernard, the editorial director at Duke Press, worked with me from the beginning to ensure that we produced a high-quality book. Two other people, Sharon Hamm and Richard Rubin, are responsible for the form and content of this book.

Sharon Hamm was the book's editor. The job of an editor is a difficult one. She had to handle the seemingly endless number of changes I kept making to the manuscript and still keep both me and the production staff on schedule. She did a great job of balancing all these responsibilities. Thank you, Sharon; it has been a pleasure to work with you.

The person who shaped the final form of this book more than anyone else was the technical editor, Richard Rubin. Many of you know Richard from his excellent technical articles, especially in the area of database design. I tend to look at the AS/400 from the inside out. Richard provided the customer view of the system. Whenever I began to get carried away with the glorification of some technical aspect of the AS/400, Richard would bring me back to reality by asking, "What does it mean to the customer?" Richard's insistence on examples for just about everything and his attention to detail make this book far more understandable to a wide audience of readers. Thank you, Richard.

Finally, this book would not have been written at all without the most important person in my life, my wife Sandra. I was having all kinds of trouble getting started. When she noted that my desk was beginning to look like

the bridge of the Millennium Falcon, she stepped in, organized my material, and transcribed the videotapes of my AS/400 architecture class. Those transcriptions formed the first draft of this book. She then took on the roles of cheerleader, counselor, reviewer, and part-time editor. Thank you for always being there for me.

I also want to thank our three wonderful sons, Mike, Brian, and Steve. In spite of their own busy schedules with work and school, they took on additional responsibilities to give me more free time, and filled in for me on numerous occasions when I needed their help. For example, during the summer months, a couple of them unselfishly volunteered to spend their weekends racing our Porsche at the various racetracks around the Midwest, so I could stay home and dedicate more time to finishing this book. Believe me, I will never be that dedicated, although my time at the track this year is down to almost nothing. I plan to remedy that situation.

--- F.S.

# **Table of Contents**

| Acknowledgments                                              | IV    |

|--------------------------------------------------------------|-------|

| Foreword                                                     | XV    |

| Preface                                                      | XVII  |

| The Revolution Begins                                        | XVIII |

| Fort Knox                                                    | XIX   |

| The Early AS/400 (aka System/38)                             | XIX   |

| The AS/400-PowerPC Union                                     |       |

| The Technical Development Team                               |       |

| The Management Team                                          |       |

| Eleventh-Hour Leadership                                     |       |

| Why This Book?                                               |       |

| How to Read This Book                                        | XXVII |

| Chapter 1: Advanced Application Architecture                 | 1     |

| Computer Architecture                                        | 2     |

| A Programmer's View                                          |       |

| Levels of Abstraction                                        | 3     |

| Software Design                                              |       |

| Architecture Classification                                  |       |

| Processor-Centric Architecture                               |       |

| Application Programming Interface (API)-Centric Architecture |       |

| High-Level Machine Architecture                              |       |

| Historical Background                                        |       |

| What's in a Name?                                            |       |

| The Rest of the Book                                         | 20    |

| Chapter 2: The PowerPC Technology                            | 21    |

| The PowerPC Alliance                                         | 21    |

| The Evolution of PowerPC                                     |       |

| The AS/400 Commercial RISC Processor                         |       |

| PowerPC Technology for the AS/400                            |       |

| The PowerPC Architecture                                     | 36    |

| Extensions to the PowerPC Architecture                  | 39  |

|---------------------------------------------------------|-----|

| A 65-Bit Processor?                                     |     |

| PowerPC AS Instructions                                 | 41  |

| AS/400 Processor Implementations                        | 42  |

| The A30 (Muskie) Processors                             | 42  |

| The A10 (Cobra) Processors                              | 46  |

| Conclusions                                             | 47  |

| Chapter 3: The Technology-Independent Machine Interface | 49  |

| Overview of the MI Architecture                         |     |

| A Non-Executable Interface                              |     |

| AS/400 Language Compilers                               |     |

| Characteristics of the Machine Interface                |     |

| Working with MI Programs                                |     |

| Creating a Program                                      |     |

| Destroying a Program                                    |     |

| Program Materialization and Observability               |     |

| Inside a Program Template                               |     |

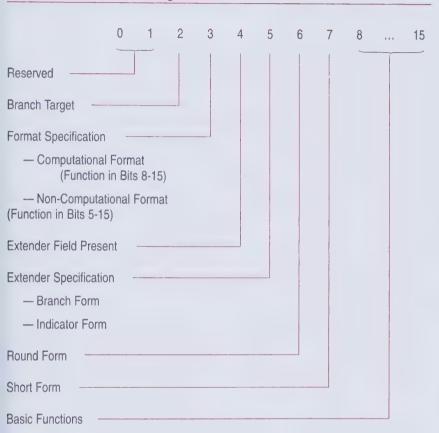

| The MI Instruction Formats                              |     |

| The MI Op-Code                                          |     |

| The Op-Code Extender                                    |     |

| MI Instruction Examples                                 |     |

| Conclusions                                             |     |

| Chapter 4: An Integrated System                         | 75  |

| The Integrated Operating System                         |     |

| Microcode                                               |     |

| System Licensed Internal Code                           |     |

| SLIC Development Environment                            |     |

| SLIC Kernel Technologies                                |     |

| System/36 Personality                                   |     |

| Something Old, Something New                            |     |

| Advanced 36                                             |     |

| Conclusions                                             |     |

|                                                         |     |

| Chapter 5: Objects and Object Management                |     |

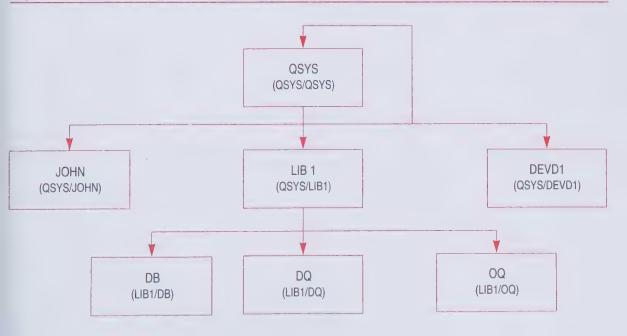

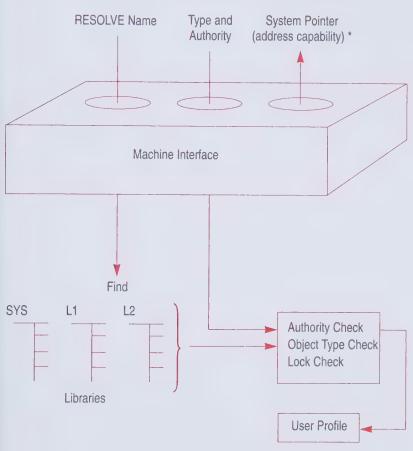

| Object Naming                                           | 93  |

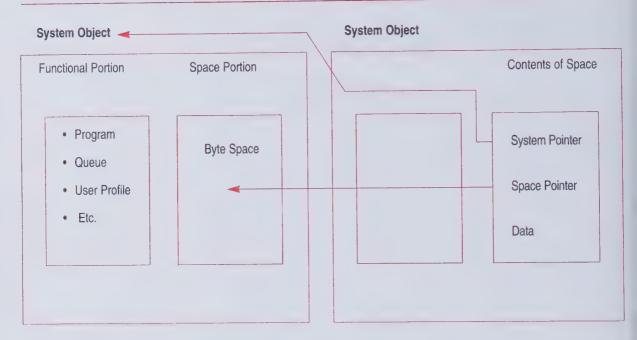

| OS/400 Objects and MI System Objects                    |     |

| Finding Objects                                         |     |

| Libraries                                               |     |

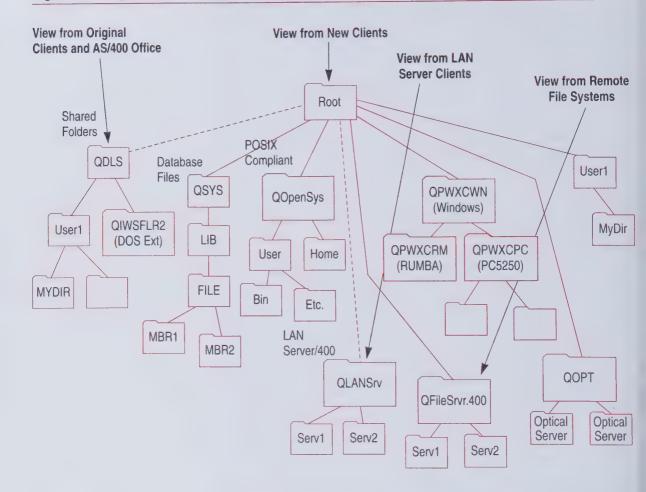

| Shared Folders                                          |     |

| Integrated File System                                  |     |

| Accessing Objects                                       |     |

| Capability-Based Addressing                             |     |

| Resolving System Pointers                               | 100 |

|    | Other Pointer Types                                     | 102 |

|----|---------------------------------------------------------|-----|

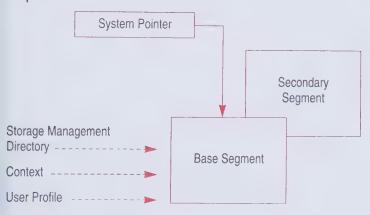

|    | System Object Characteristics                           | 105 |

|    | Program Objects                                         | 106 |

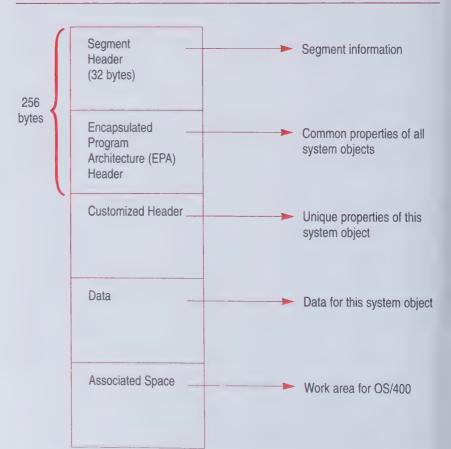

|    | Inside a System Object                                  |     |

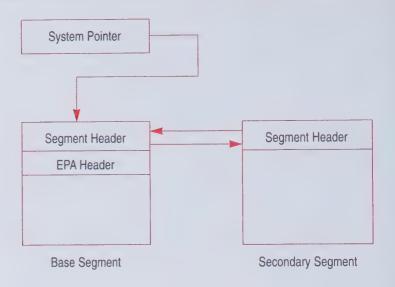

|    | Segmented Memory                                        |     |

|    | System Object Structure                                 |     |

|    | Multisegment Objects                                    |     |

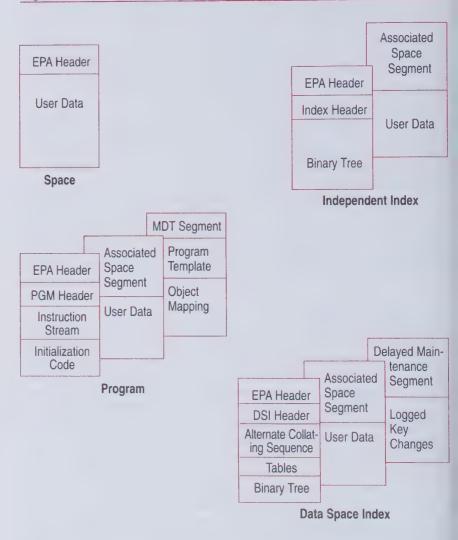

|    | Contents of the Headers                                 |     |

|    | Segment Headers                                         |     |

|    | EPA Headers                                             |     |

|    | Examples of Objects                                     |     |

|    | Conclusions                                             | 117 |

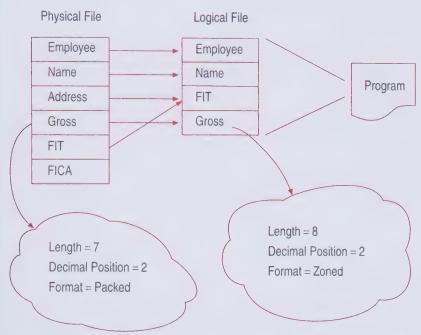

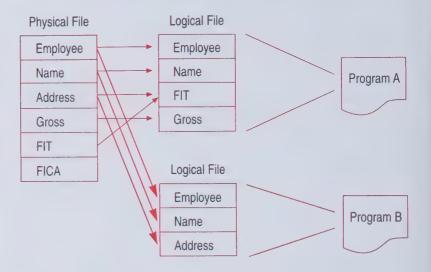

| CI | hapter 6: The Integrated Database                       | 119 |

|    | Relational Database Evolution                           |     |

|    | The Two Faces of Database                               |     |

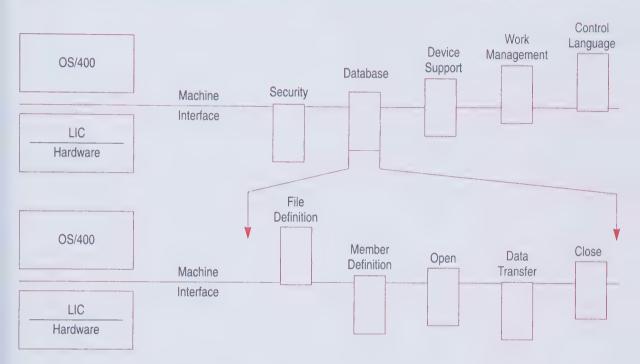

|    | Overview of Database Operations                         |     |

|    | Functions of a Database Management System               |     |

|    | Data Description and File Creation                      |     |

|    | Creating Physical Files and Tables                      |     |

|    | Creating Logical Files and Views                        |     |

|    | Data Dictionary and Catalogs                            |     |

|    | Data and Program Independence                           |     |

|    | Data Security                                           |     |

|    | Data Integrity and Recovery                             |     |

|    | Journaling                                              |     |

|    | System-Managed Access Path Protection                   |     |

|    | Commitment Control                                      |     |

|    | Triggers                                                |     |

|    | Referential Integrity<br>High-Availability Disk Systems |     |

|    | Other Database Functions                                |     |

|    | Stored Procedures                                       |     |

|    | National Language Support                               |     |

|    | Predictive Query Governor                               |     |

|    | Database Performance Enhancements                       |     |

|    | Distributed Databases                                   |     |

|    | Gateways to Other Databases                             |     |

|    | DataPropagator for OS/400                               |     |

|    | OptiConnect for OS/400                                  |     |

|    | Parallel Databases                                      |     |

|    | Symmetric Multiprocessing (SMP) Parallel Database       |     |

|    | Loosely Coupled Parallel Database                       | 141 |

|    | * * * * * * * * * * * * * * * * * * *                   |     |

|    | Implementation of Database Functions            | 141   |

|----|-------------------------------------------------|-------|

|    | Database Objects                                | 142   |

|    | Data Spaces                                     | 142   |

|    | Data-Space Indexes                              | 143   |

|    | Cursors                                         |       |

|    | The User's Path to Data                         |       |

|    | SLIC Journaling                                 |       |

|    | Commitment Control in SLIC                      |       |

|    | Machine Indexes                                 |       |

|    | Binary Searches                                 |       |

|    | Binary Radix Trees                              |       |

|    | Internals of a Binary Radix Tree                |       |

|    | Conclusions                                     | 155   |

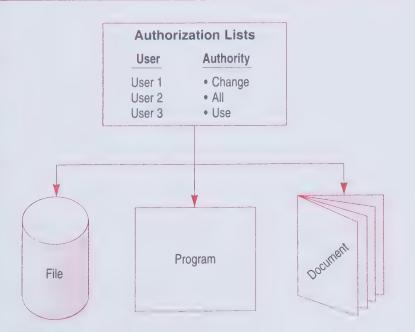

| Cł | napter 7: Security and Authorization            | 157   |

|    | Integrated Security                             |       |

|    | System Security Levels                          |       |

|    | Level 10 — No Security                          |       |

|    | Level 20 — Password Security                    | 159   |

|    | Level 30 — Resource Security                    | 160   |

|    | Level 40 — Operating System Security            | 161   |

|    | Level 50 — C2 Level Security                    | 162   |

|    | User Profiles                                   | 162   |

|    | User Class                                      |       |

|    | Objects Owned and Authorized                    |       |

|    | Authorization of Objects                        |       |

|    | Privileged Instructions and Special Authorities |       |

|    | Program Adoption of Authority                   |       |

|    | Grouping Authority                              |       |

|    | Authority Search Algorithm                      |       |

|    | Conclusions                                     | 169   |

| Cł | napter 8: Single-Level Store                    | 171   |

|    | How Many Bytes Does 64 Bits Address?            |       |

|    | The Single-Level Store in Rochester             |       |

|    | Virtual Memory                                  |       |

|    | Virtual Memory for Timesharing                  |       |

|    | A Single-Level Virtual Memory                   |       |

|    | Persistent Virtual Memory                       | . 178 |

|    | Overview of Single-Level Store                  | . 181 |

|    | Performance Implications of Single-Level Store  | . 186 |

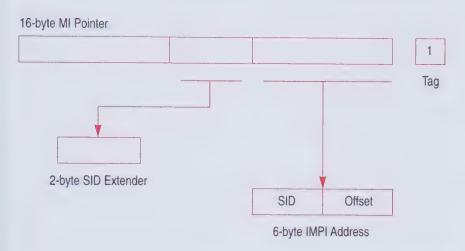

|    | Pointers and Tags                               | . 190 |

|    | Hardware Protection for Pointers                | . 191 |

|    | Tags-Active Mode                                | . 193 |

|    | Pointers and Tags on Disk                       | . 194 |

|    |                                                 |       |

| Inside a Pointer                       |       |

|----------------------------------------|-------|

| A Tale of Two Address Sizes            | . 196 |

| Running Out of Addresses               |       |

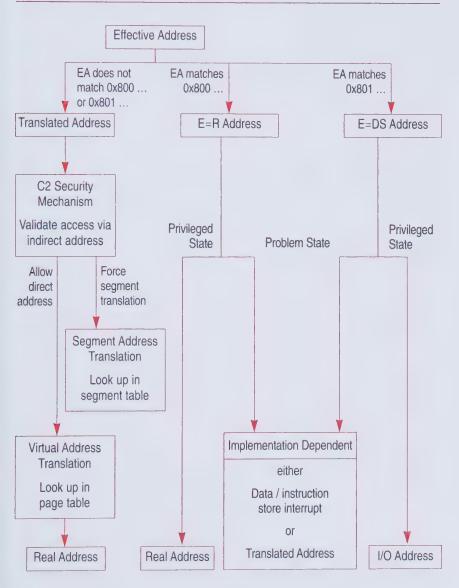

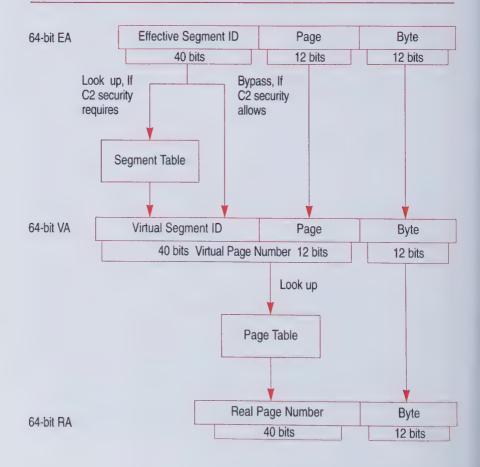

| Address Translation                    | . 202 |

| Memory Model Characteristics           | . 202 |

| Machine State Register                 | . 202 |

| Address Translation Overview           |       |

| Virtual-to-Real Address Translation    | . 207 |

| Hashing                                | . 208 |

| Page Table Entry                       | . 210 |

| Memory Access Modes                    | . 212 |

| Page Protection                        |       |

| Disk Management                        |       |

| Auxiliary Storage Pools (ASPs)         |       |

| Storage Segments                       |       |

| Disk Extents                           |       |

| Access Group Segments                  |       |

| Auxiliary Storage Directories          |       |

| Conclusions                            | . 219 |

| Chapter 9: Process Management          | . 221 |

| The World's Greatest Tasking Structure |       |

| Microkernel Technologies               |       |

| Starting at the Bottom                 |       |

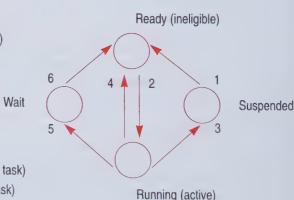

| Task Dispatching in the AS/400         |       |

| The States of a Task                   |       |

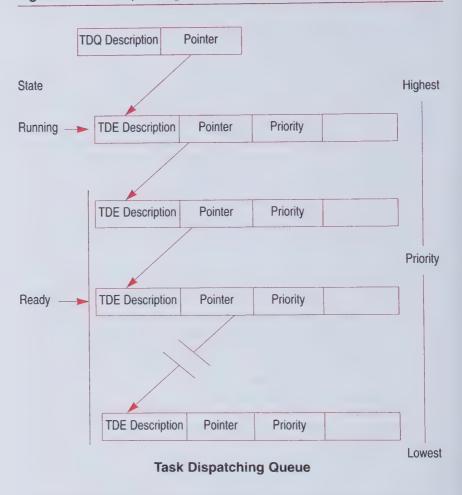

| Task Dispatching Queue                 | . 227 |

| Send/Receive Queues and Counters       | . 229 |

| Multiprocessor Considerations          | . 231 |

| Symmetric Multiprocessing              | . 231 |

| Asymmetric Multriprocessing            | . 233 |

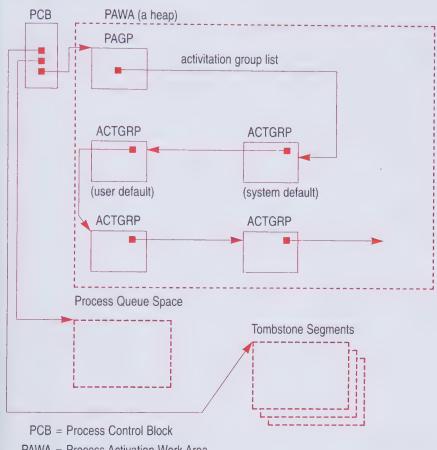

| MI Processes                           | . 233 |

| Original Process Model                 |       |

| ILE Process Model                      |       |

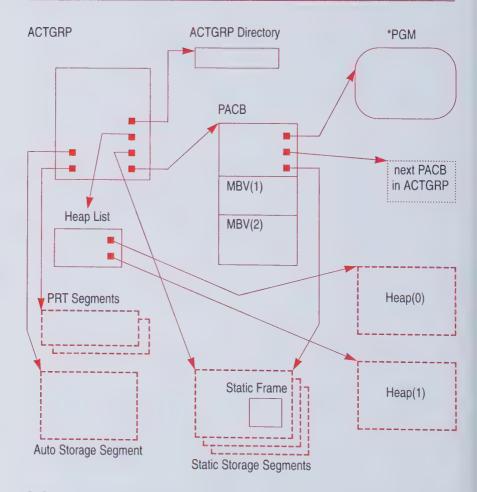

| Inside an ILE Process                  |       |

| ILE Process Structure                  |       |

| ILE Activation Group                   |       |

| Exceptions, Events, and Interrupts     |       |

| Exceptions and Events at the MI        |       |

| SLIC Exception Management              |       |

| Hardware Context Switching             |       |

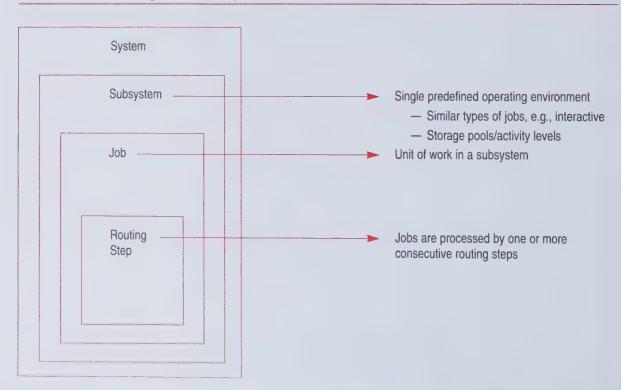

| Work Management and OS/400 Jobs        |       |

| Work Management Concepts               |       |

| Subsystems                             | . 249 |

|     | Original and New Job Structures                        | 250 |

|-----|--------------------------------------------------------|-----|

|     | Processes, Tasks, Jobs, Activation Groups, and Threads |     |

|     | Conclusions                                            |     |

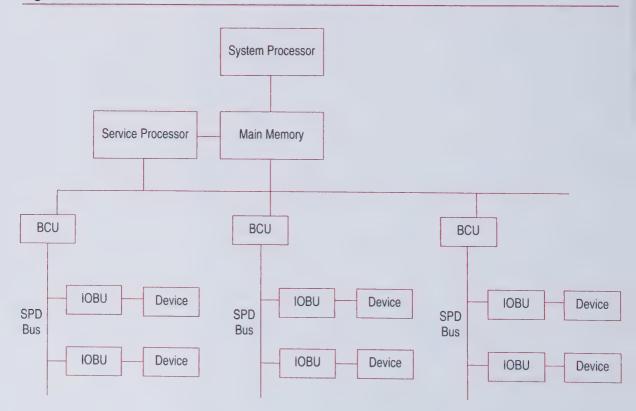

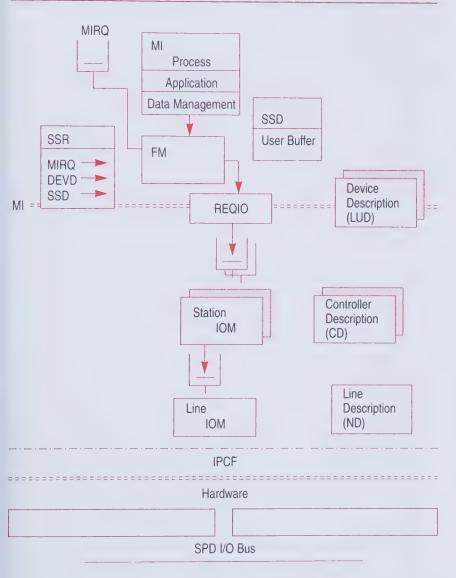

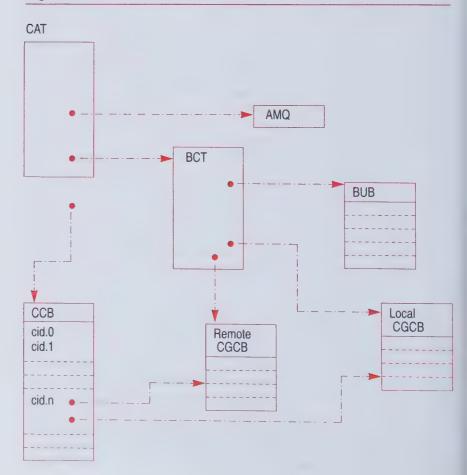

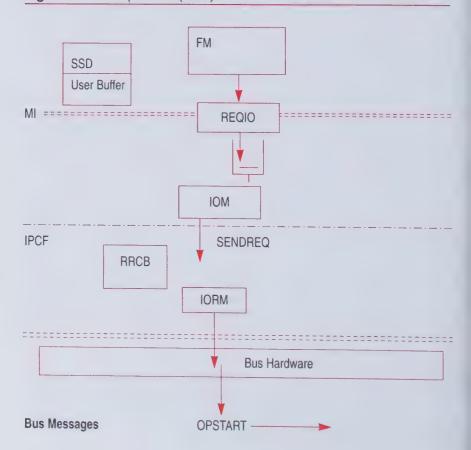

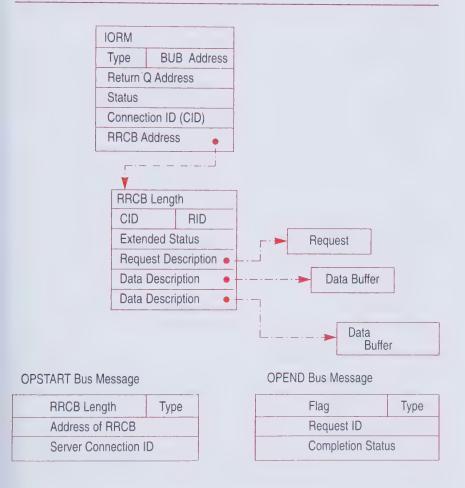

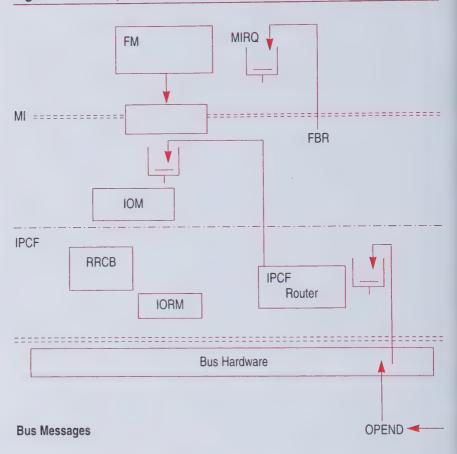

| Ch  | apter 10: The I/O System                               | 253 |

| UII | Historical Perspective                                 | 254 |

|     | The Fort Knox Project                                  | 255 |

|     | The Silverlake Project                                 | 257 |

|     | Hardware I/O Structure                                 |     |

|     | I/O Hardware Connections Using Fiber Optics            |     |

|     | I/O Bus Operations                                     |     |

|     | I/O Operations on the AS/400                           |     |

|     | Objects to Support I/O                                 |     |

|     | The Components of I/O                                  |     |

|     | Putting It All Together                                |     |

|     | Conclusions                                            |     |

|     |                                                        |     |

|     | apter 11: Client/Server Computing                      |     |

|     | The Next Generation in Business Computing              |     |

|     | What Is Client/Server?                                 |     |

|     | Models of Client/Server Computing                      |     |

|     | Transformation of the AS/400                           |     |

|     | Client Access for OS/400                               |     |

|     | 5250 Emulation                                         |     |

|     | Print Serving                                          |     |

|     | Mail/Office Offerings                                  |     |

|     | Data Serving                                           |     |

|     | Client Management                                      |     |

|     | Programming Interfaces                                 |     |

|     | Application Interfaces                                 |     |

|     | Program-to-Program Communications                      |     |

|     | Messaging Interfaces                                   |     |

|     | Multimedia Enablers                                    |     |

|     | File Server I/O Processor                              |     |

|     | AS/400 Advanced Server Models                          |     |

|     | Application Enabling for Client/Server                 |     |

|     | Distributed Objects in a Client/Server Environment     | 300 |

|     | Application Development Environments                   | 301 |

|     | SOM and DSOM                                           | 301 |

|     | Application and System Frameworks                      |     |

|     | Application Environments                               | 304 |

|     | OpenDoc                                                |     |

|     | Taligent                                               |     |

|     |                                                        |     |

| WebConnection for OS/400                               |   |

|--------------------------------------------------------|---|

| Conclusions                                            |   |

| Chapter 12: The Future of the AS/400                   |   |

| Future Processor Technologies                          |   |

| AS/400 RISC Processor Road Map                         |   |

| Beyond RISC                                            |   |

| The Challenge of VLIW Technology                       |   |

| History of Long Instruction Word Machines in Rochester |   |

| VLIW for AS/400                                        |   |

| The Future of Multiprocessor Systems                   |   |

| Multicomputer Clusters                                 |   |

| Symmetric Multiprocessing                              |   |

| Firmly Coupled Multiprocessing                         |   |

| The Future of AS/400 I/O                               |   |

| Future IOP Technology                                  |   |

| Disk Arrays                                            |   |

| Future AS/400 Software Technologies                    |   |

| Microkernels                                           |   |

| Workplace Technologies                                 |   |

| Application Engines                                    |   |

| The AS/400 in the 21st Century                         |   |

| Technologies                                           |   |

| Client/Server                                          |   |

| Application Development                                |   |

| Conclusions                                            |   |

| Index                                                  | 1 |

|                                                        |   |

# **Foreword**

IBM's AS/400 is one of the most interesting and effective commercial computer architectures ever introduced. Long before "object-oriented" had become a familiar concept, the AS/400's high-level machine interface (introduced by the System/38, the AS/400's predecessor), presented the application developer with a set of objects, such as queues, indexes, and database files, that could be used as application building blocks. These objects provide a great degree of system functionality in a highly consistent and easily used form. The uniform object interface hides details from the AS/400 programmer so he or she can ignore the often complex control blocks and system routines that comprise the operating system internals. Further, the operating system can limit access of objects to well-defined operations, thus providing additional runtime application protection.

AS/400 objects are implemented with a layer of software over the hardware; this layer lets IBM make substantial changes to the hardware with relatively low impact on applications. For the most part, new hardware can be introduced with only an update of the internal code IBM provides, because the object interfaces, which are used by applications, remain the same. And therein lies another benefit of AS/400 objects: they let applications take advantage of major hardware advances without the need for the programmer to modify the application code. All the implementation details of system objects used by applications are "hidden" in this layer of software.

Programmers become spoiled by the AS/400's architecture — where else will you find such a rational approach to system function? But by nature, programmers ultimately want to know how things work, and AS/400 programmers are no exception. At every conference or user group I attend, I'll find a group of AS/400 programmers sharing lore about what goes on internally when you activate a program object, override a file open, or perform some other operation on a system object. This pursuit of what goes on under the covers of the AS/400 isn't merely to satisfy intellectual curiosity;

in many cases, a deeper understanding of the AS/400 architecture lets a programmer write more functional or faster code. But as any experienced programmer knows, you can't learn everything from the manuals; and this is especially true for the AS/400, since the manuals expressly avoid details about internal structure or operations.

Consequently, despite widespread appreciation for how the AS/400 hides details under its high-level machine interface, many of us have long wanted a book such as *Inside the AS/400*. This book provides clear — and thorough — explanations of all the AS/400 architecture's important components. Any AS/400 programmer will find *Inside the AS/400* essential to his or her technical understanding of the AS/400.

Of course, my curiosity about the AS/400 isn't limited just to its current technical underpinnings — and I suspect the same is true for other AS/400 developers. I'm intrigued by the technical and business *processes* that gave birth to such an advanced system — and curious about the individuals who have been involved behind the scenes. I also have a vested interest in knowing where the AS/400 is headed for the future.

Fortunately, Frank Soltis is just the person to give the real "inside" stories for all three AS/400 areas: its technology, its history, and IBM's future plans. Frank has been one of the central figures in these stories since the first day the S/38 was conceived, and he has played key roles in the evolution of the AS/400 architecture. His experience has spanned several major eras in IBM organization and technology, and his responsibilities have included hardware, software, and business domains. Frank also combines an academic career teaching computer science with his responsibilities as an engineer and system architect. Leaven all this talent and experience with a bit of Minnesotan humor, and you have the perfect guy to make topics like "tagged memory" and "task dispatching queues" an interesting read.

When I first met Frank in 1985, he didn't strike me as the traditional IBMer — but then again, I'd just been introduced to the S/38 after years working with IBM mainframes, and the S/38 itself seemed refreshingly different, too. Frank spent hours filling me in on technical details of the S/38 architecture, as well as much of the personal side of S/38 history. Frank explained technical concepts so clearly — and was such an entertaining story teller as well — that I encouraged him to write a book about the S/38. Only later did I learn that, as far as IBM headquarters was concerned, the future of the S/38 was up in the air at that time. Understandably, Frank waited to tell the story until he was assured it would have a happy ending. With the great success the AS/400 has experienced, and with its ever-widening use and key strategic role for IBM, the time is right for Frank to share his insight and stories with us all. This is truly the best guided tour of the AS/400 around.

Paul Conte President, Picante Software, Inc.

# **Preface**

"Welcome to Rochester," reads the sign in the airport, "where the winters are cold and the computers are hot." Rochester, Minnesota, is the home of IBM's Application System/400 (AS/400). Since its introduction in 1988, the AS/400 has become the world's most popular multiuser computer system.

I first saw Rochester in 1962 while I was still a university student. IBM had offered me one of the first two summer jobs in its year-old Rochester development laboratory. One of the jobs was working on a joint medical project with the Mayo Clinic. The manager of this project had been the customer engineer who worked on the IBM equipment used in my father's business. At the time, I had no interest in computers and even less interest in living in a small prairie town in southern Minnesota. The lure of the aerospace industry in California tempted me. However, I knew the project manager in Rochester and thought it might be fun to work for him during the summer.

When I arrived in Rochester, I received some bad news. The other summer hire who arrived a week before me had taken over the medical development job. I was going to work on the development of a banking terminal. This was not a good start, and it was too late to go somewhere else. I had already turned down other summer job offers. Besides, I needed the money and still believed that having IBM on my resume would look good to future employers, so I took the job.

The enthusiasm of the people I met in Rochester was contagious. The manager of the bank terminal project must have heard I was disappointed about not getting the medical job. He spent a great deal of time with me that summer talking about Rochester's future. He was convinced computers were a big part of that future, and Rochester would need people with intimate knowledge of computer design. He convinced me, and soon I began to think differently about computers.

I returned to school with a newly discovered interest in these electronic marvels. Most of my studies after that summer focused on digital computer

design. The following year, when I graduated and it was time to find a permanent job, I could not resist the draw of this dynamic laboratory in Rochester. I signed on as an IBM employee working for the same project manager I had worked for the year before.

Before long, I again found myself back in school pursuing a doctorate degree. Rochester needed people who understood computer architectures. Most of us were engineers with little experience in the software arena, and my prior training was in electrical engineering. So at Iowa State University I concentrated on studying computer architecture and operating system design.

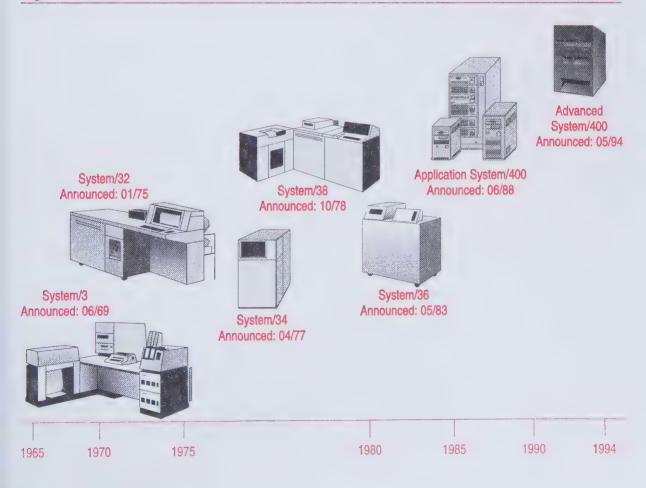

I returned to Minnesota late in 1968 and began to work on an advanced computer design. I arrived in time for the announcement of Rochester's first computer in June 1969, the IBM System/3. The System/3 was a special-purpose product that looked more like an accounting machine than a computer. I didn't realize it at the time, but the group at Rochester had managed to get into the computer business by telling IBM they were building an accounting machine. That didn't seem to matter much, because the System/3 went on to be the first in a line of successful products that would revolutionize commercial computing. In late 1969, I got a new job assignment. I was to design the architecture for the successor to the System/3.

#### **The Revolution Begins**

On a bitterly cold Thursday, January 8, 1970,¹ I presented to Rochester management a proposal for a revolutionary new computer architecture. A high-level machine interface was a fundamental part of that proposal. The addressing structure for the architecture, called single-level store, had evolved from my Ph.D. dissertation work. The driving motivation behind the architecture was to protect the customer's investment in application software by delivering a computer system that was independent of the underlying hardware technologies. This system was very different from a System/3, but it did contain most of the System/3 functions. This capability to have a "System/3 environment" would prove to be valuable years later when we needed to merge the two product lines.

Though many ideas behind the new architecture were truly radical, Rochester's management was willing to accept the proposal and to form a special group in the development laboratory to pursue the new system. Within six months, an organization of nine people formed to make the proposal a reality. My role was to be the architect for this new system. Little did I realize then that I would continue in this role for more than 25 years.

The Advanced Systems organization formed to create the new system stayed separate from the System/3 development effort (the System/3 family continued to grow with the addition of the System/32 in 1975 and the System/34 in 1977). Staffing for the new system did not start in earnest until the middle of the 1970s. Soon, hundreds and then thousands of people

<sup>1</sup> A wonderful trivia question is to ask for the name of two famous celebrities whose birthday is January 8th. The answer is Elvis and the AS/400. Elvis Presley was born in Tupelo, Mississippi, on January 8, 1935 and the AS/400 was born in Rochester, Minnesota, on January 8, 1970.

throughout IBM joined the team. On October 24, 1978, we announced the new system. We called it the System/38.

The System/38 was immediately heralded as an advanced architecture computer. It was easily the most innovative design IBM had announced in many years. Few people either inside or outside IBM fully understood this new system. A cult-like following quickly formed among those customers who did understand its power and potential. User group meetings often took on the appearance of a religious rally.

The System/38, however, never did replace the System/3 family in the way we originally envisioned. It was a new system that did not attract many of our installed customers. The first shipments of the System/38 were delayed until July of 1980, because we said it had performance problems. Actually, the system wouldn't run for any extended period of time before crashing — the ultimate performance problem. This delay scared off some of our existing customers. Also, customers of the smaller System/32 and System/34 found the new system to be too large and too expensive. In May of 1983, the last variant of the System/3, the System/36, was announced to satisfy these customers' needs. Rochester would continue to have two distinct lines of computers.

#### **Fort Knox**

In the early 1980s, IBM decided to create a new converged system it called Fort Knox. The intent was to replace five incompatible IBM product lines, including the two from Rochester, with Fort Knox. Customers who owned any of the five machines would be able to move their applications to this single system. The development of Fort Knox started with major investments in four different IBM laboratories.

By 1985, it was clear that Fort Knox was in trouble. Many of us in Rochester believed it was doomed from the beginning, because it was trying to solve an IBM problem rather than a customer problem. Others in IBM saw it as technically too big an undertaking: There was no way to converge five separate systems into one. Still others thought it was impossible to manage the project across the four laboratories. For all these reasons, it failed; and IBM terminated the project.

Fort Knox siphoned off most of the development resources that would otherwise have been put into the System/36 and the System/38. This made it difficult for either system to remain competitive. Further, IBM had gone so far as to declare the System/38 as "non-strategic" and discouraged customers from buying this system. Consequently, Rochester lost an enormous amount of business to competitors.

#### The Early AS/400 (aka System/38)

Late in 1985, a small group of developers in Rochester demonstrated that software for the System/36 could run as an environment on the System/38.

We even changed the name of our operating system for the AS/400 to Operating System/400 (OS/400). To this day, many of our developers still call it XPF. XPF stands for Extended CPF. Control Program Facility (CPF) was the name of the System/38 operating system. The cost of hardware technologies had come down so that we could now build small models of the System/38. This meant we could cover the entire Rochester product range. The proposal to combine the two systems into a single machine based on the System/38 quickly followed. We named this new machine Silverlake and convinced IBM management we could build it.

Once again, it was Rochester's turn to show IBM and the whole computer world what it could do. After an unprecedented 28-month development cycle, we were ready to announce the converged system. We told the world it was a new system and called it the AS/400. Insiders, however, know that under the covers of every AS/400 lurks a System/38.<sup>2</sup>

The AS/400 was an immediate success. Not only did it take back the market share lost to competitors in earlier years, but it also quickly surpassed all of them. There are more than 300,000 AS/400 systems running businesses all over the world, making the AS/400 the best-selling, multiuser computer system ever. The System/38 cult had become a full-fledged religion.

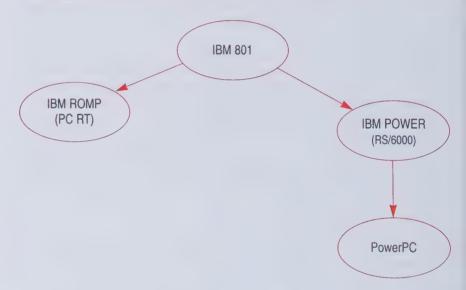

In 1991, Apple Computer, Motorola, and IBM reached an historic agreement to develop a new family of processors. These processors would be used in everything from hand-held devices to supercomputers. Called PowerPC, these new processors were poised to take the computer world by storm. At the time, Rochester was looking at a new processor design for the next generation of AS/400 systems. This was to be the first totally new design since the 1978 processor used in the original System/38. Why not join forces with the PowerPC alliance to create the new AS/400 processor based on this design?

#### The AS/400-PowerPC Union

I led a team of people from Rochester to identify the requirements for the AS/400 processor. We then worked with the PowerPC architects and designers to create a 64-bit processor based on the PowerPC architecture. Processors built to this new architecture should take the AS/400 well into the next century.

The introduction of these new PowerPC processors, optimized for the AS/400, marks a milestone in the AS/400's history and demonstrates the power of the AS/400 architecture. Other computer system vendors are planning to move their systems to new processor designs with mixed emotions. Those currently making the transition are causing major disruptions to their existing customers. Application software must be recompiled or rewritten. Operating systems also must be rewritten to take advantage of the new processors. The result is that most vendors are reluctant to use the latest processor technologies. In contrast, the AS/400 architecture's technology-independent nature makes it relatively easy for an existing customer to incorporate the new processor technologies.

The use of common hardware technologies is important, but there is greater significance to this announcement. Now the potential exists to have application and operating system software from other IBM and

non-IBM systems run on the AS/400. The future benefits to AS/400 customers are enormous.

A question often asked is, "How did the AS/400 come about, and who were the people responsible for this system?" We will cover more of the AS/400 history and identify some of those people who were involved as we go through this book. There are, however, a few key technical and management leaders without whom this system would never have been created.

#### The Technical Development Team

IBM likes to promote the development of any new product as a team effort with everyone contributing. In truth, a small handful of technical and management leaders with the foresight, creativity, and drive usually make a product successful. Such leaders are responsible for the development and success of both the System/38 and the AS/400.

Rochester has had many good technical and management leaders but only a few true visionaries. A visionary leader not only has a vision of what is possible but also has the ability to convey that vision to others. A visionary leader is able to give away the ownership of that vision to everyone involved. Soon the vision takes on a life of its own as it grows and takes shape. The leader's role becomes one of a cheerleader, encouraging everyone to excel with his or her part of the vision.

In 1972, I was still struggling to sell the radical concepts of the System/38 architecture to our developers. The engineering organization was making progress on the hardware design primarily because most of them thought they were just building System/370 hardware with some new software on top. The format of the internal instructions in the System/38 looked very much like that used in a System/370. This was no coincidence. It was the only way to get the engineers on board and comfortable that they were not doing anything unusual.<sup>3</sup>

Little progress was evident on the software front. Most of our programmers in Rochester were busy building better versions of the System/3 software. They were comfortable with the System/3 design and wanted no part of a revolutionary new architecture.

It was during this time that two individuals stepped forward to help create the total architecture and to help convince the entire development community that we were on the right track. Dick Bains and Roy Hoffman are two of the most creative, truly visionary people I have ever met. They were also true believers. During 1972, the three of us completed the definition of the AS/400 architecture, and though some of the details changed in the following years, none of the concepts have.

Dick's talents were in compiler technology and languages. His expertise was critical to the definition of the high-level machine interface and the internal translator. He had grown up in the neighboring state of Wisconsin. Before joining IBM in Rochester, Dick held several different jobs. At one point he

<sup>3</sup> In later years, people would come to Rochester, see this instruction format, and declare the System/38 was built on a System/370. IBM even funded projects to make the System/38 software run as an operating system on System/370 hardware. These projects all failed.

was a ski instructor in Aspen, Colorado. Whenever things were not going well with our architecture definition, Dick would long for the simpler life of a ski instructor. Thankfully, he never followed through on those longings.

Dick was always one of those individuals who could get so involved in solving a problem he would do something without necessarily thinking about the consequences. For example, a year earlier, Dick was trying to convince management that some of the site's computer systems had a security problem. When no one would listen to him, he decided to demonstrate the problem by going into a system to which he was not authorized and leave a message for those responsible for the system to call him if they wanted to close the security exposure. He managed to unintentionally overwrite some files and almost lost his job. Fortunately for all of us, management recognized his talents and he kept his job. He also made his point.

To this day, Dick still has these same qualities. When he sees something that needs to be done, he doesn't stand on formalities; he just does it. His breadth of knowledge on the AS/400 and his ability to work closely with customers to solve both technical and business problems keeps him in high demand. Dick remains one of the key technical leaders on the AS/400.

Roy at that time was an engineer with expertise in computer architectures and operating system designs. His contributions, especially in the low-level operating system functions, made the System/38 architecture a success. Roy had grown up on a farm just outside of Rochester. Like many young men, he had chosen to leave home to attend college and find a job. He had worked for another computer company for a while; but after finishing his Ph.D., he had returned to Rochester to work for IBM. On weekends, you could find Roy riding through the countryside on his motorcycle. We would have long discussions about the merits of motorcycles versus sports cars, my hobby (I have always preferred to have a roof or a roll bar over my head).

Roy was always very good at solving technical problems. He has a tremendous knowledge of computer systems and can attack a technical problem from a vantage point most of us do not have. His new view often led to the technical solution; helping others with technical advice has always been one of his real strengths. (In fact, Roy didn't stop at technical advice. He often gave those of us around him personal advice as well, whether we wanted it or not. He would take great delight in analyzing and giving advice on subjects for which he had no experience.)

After his work on the System/38, Roy led some of the advanced technology work in Rochester. He also worked on new technologies for all of IBM. Roy was a member of the IBM Academy that was responsible for helping set technical directions in IBM. In 1994, he retired from IBM. Roy is now teaching at a local university and writing a technical book. On a nice day, you will still find him out riding his Harley-Davidson.

Somehow, the combination of a ski instructor, a motorcycle enthusiast, and a car nut worked. By the end of 1972, the design of the architecture was

whole. In the following years, Dick, Roy, and I would often get together to discuss changes and new ideas. To this day I am amazed that many of the ideas we collectively put into the system are just now being discovered by others in the computer industry.

Rochester has been blessed with good technical leaders. The many innovations in both hardware and software are testimony to these people. None of the others, however, has had the same vision and foresight for the system as did Dick and Roy. They clearly saw the future. Like so many technical leaders who usually work behind the scenes and are seldom visible outside of their own organizations, these two have never received the recognition they deserve.

#### The Management Team

No system can be successful with only technical leadership; management leadership is also critical. In my opinion, four management leaders envisioned the System/38 and the AS/400 and then created the environment in which it could be built. One of them, above all others, needs to be recognized: Harry Tashjian saw the need for a small, easy-to-use business system and created a new market for computers. Without his vision, there would be no Rochester-developed computers.

Harry was the management force behind the System/3, System/32, System/34, System/36, and System/38. He was originally the system manager for all of these products and later became the director of the Rochester laboratory. It was Harry's vision that transformed Rochester from an obscure, insignificant little facility in the middle of a Minnesota cornfield to a world leader in the development of business computer systems.

It was also Harry Tashjian, manager of the bank terminal project, who convinced me to pursue computers that first summer many years ago. I still remember our long talks about Rochester's potential for developing new computer systems. Harry encouraged me to return to school to study computer architecture. When I returned to Rochester, he was the one who gave me the assignment and the support to design the architecture of the System/38, which would become the AS/400. Without Harry, there would be no AS/400.

In addition to Harry Tashjian, two other management leaders made the System/38 a success. Ray Klotz was our engineering manager and my boss for most of the project. In 1970, Harry put Ray in charge of the initial development team of nine people. Ray had a strong hardware background, having led a System/360 processor development in Endicott, New York, before coming to Rochester to lead the System/3 hardware effort.

Ray's initial vision for the System/38 was less ambitious than what some of us had in mind. He would sometimes remind us that the entire System/3 hardware only required 3,000 circuits, and he would ask why we needed so many more. He liked to challenge us on our technical decisions until he was convinced we had looked at all of the options. Then he gave us the freedom

to take ownership of the design and let us make our own decisions. Whenever we got into trouble, he was always there to support us and help us find the way out.

Ray was very much a father figure for most of us. We all jumped whenever he raised his voice, which he did often. But under his gruff exterior was a tremendously caring individual who demanded perfection from each of us, and he usually got it.

Gaylord Glenn Henry was the most brilliant, and totally outrageous, manager I have ever known in IBM. To say that Glenn did not fit the role of a typical, conservative IBM manager is an understatement. The scruffy beard, the often mismatched clothing, and the six-packs of Tab in the pink cans he carried everywhere identified him as a unique individual. Glenn came from the IBM laboratory in Boca Raton, Florida, in 1972 to be the programming manager for the System/32 and then the System/38. He was an intense individual with tremendous personal drive that inspired everyone around him.

Glenn was a con artist who could convince developers and managers alike to follow him. When seemingly unsurmountable problems arose, Glenn convinced all of us that he had everything under control. Soon, a solution to the problem would appear and Glenn would just smile. Without his talent and vision, the System/38 development likely would have been terminated on numerous occasions.

I miss the shouting matches between Glenn and Ray. When they disagreed, the walls would shake. It was fun to watch the two argue, especially when you knew neither could support the position he was arguing (on occasion, Harry would join in, but more often he would let them settle their own disagreements). They did, however, both agree on one thing: We were going to build the best computer system the world had ever seen. The System/38 was a tribute to these two strong-willed individuals.

After the System/38 was announced, we lost all three of these leaders. Harry Tashjian left Rochester to lead a new start-up company for IBM called Discovision. After Discovision, he directed other activities within IBM before retiring with 38 years of service. Glenn transferred to Austin, Texas, to take over the development effort for the PC-RT. He left IBM in 1988 after 21 years, disgusted with the organization's inability to integrate new ideas. Not surprisingly, some of his ideas are just now being incorporated into IBM products. Glenn's leaving was a major loss for IBM. Ray saw the System/38 announced, but died before seeing the full impact his system would have on the entire computer industry. No one has ever been able to take his place.

#### **Eleventh-Hour Leadership**

Without a visionary leader, Rochester's computer systems faltered in the early 1980s. We did, however, have some strong managers who understood the value of the systems we built. Through often devious means, these

individuals managed to keep our systems alive. Still, it seemed we did not have much of a future as we continued to lose business to competitors. Fortunately, someone stepped in at the eleventh hour to pull us out from near oblivion. His name was Tom Furey.

Tom has always been a master salesman. He knew how IBM worked internally and managed to convince the corporation that Rochester systems were strategic to IBM's future. He then set about to convince all of us to put in the extraordinary effort required to get a new system out the door in record time.

Tom also understood marketing and customer requirements. He transformed Rochester from a product-driven to a market-driven organization. He first got our customers directly involved with development. Customer councils had a big say in making system trade-off decisions, and the result was a system for which many customers felt personal ownership. Rochester would later win the prestigious Malcolm Baldrige National Quality Award for this market-driven effort.

True leadership is often only recognized in hindsight. Tom was not a technical leader as some of his predecessors had been, and many in the laboratory didn't recognize the leadership he provided. Our technical people didn't think he fully understood what they were doing. He didn't, but it also didn't matter. For example, Tom never understood that the AS/400 was a repackaged System/38; or if he did, he never let on. He told everyone outside of Rochester it was a totally new system from the ground up, and they believed him.

The early commercial success of the AS/400 is clearly due to Tom's leadership. He orchestrated the biggest product launch IBM had seen since the System/360. This launch propelled the AS/400 to the front of the multiuser commercial market. After Rochester, Tom moved to Santa Teresa, California, to be the general manager for the development of IBM's DB/2 database. Later, he became the general manager for client/server computing in IBM.

#### Why This Book?

The time is ripe for a book on the inner workings of the AS/400. IBM has never before provided an in-depth look at the design, architecture, and history of this remarkable system. Neither has it explained how the AS/400 can do the things it does. My goal in writing this book is to demystify the AS/400 and perhaps shed some light on how this system came to be.

As you might already have sensed, I feel a strong responsibility to include in this book some historical information. A few years back, I informally inherited the position as Rochester's resident historian from its originator, Carl Gebhardt. Carl was our business manager for the early systems and later became the system manager for both the System/34 and the System/38 when Harry Tashjian was the laboratory director. Carl was responsible for the financial success of Rochester's early systems. I worked for Carl in the early 1980s when he was our director of strategy. Carl was a Rochester

landmark, having been here for many years. If you ever had a question about something that had happened in Rochester several years earlier, chances are Carl knew the answer. He would often introduce himself as Rochester's resident historian (there was no official resident historian, but both of us thought there should be). When Carl retired, we discussed who should take over this unofficial position, and he passed the title on to me.

This book is written for those who want to know more about the AS/400. It is not a specification written for operating system designers who need far more detail than that documented in these pages. Neither is it a rehash of IBM product announcement material. It is written for customers, application developers, and students who want to understand how the AS/400 works so they can make business decisions, write better applications, or simply see what makes this system tick. Is it magic, or just good design? Perhaps it's a little of both.

I need to point out that the views expressed in this book are my own. I am unashamedly an AS/400 bigot. My views are not necessarily the official views of the IBM Corporation. I hope you enjoy reading this book about the AS/400 as much as I enjoyed creating it.

# **How to Read This Book**

An explanation of how to read this book may seem strange, but there is good reason. The intended audience is reasonably broad, ranging from business executives who want to know how an AS/400 can benefit their business to "bit-head techies" who want to understand minute design details. I wrestled with how to satisfy such diverse interests. I considered splitting the book into two parts, one part giving an executive overview and the other part offering the technical details. But that organization is difficult for someone who needs business benefits and first-level technical details. I also considered putting a road map into the book, recommending which sections should be read by executives, application developers, students, or bit-heads, respectively. I decided against this approach because the classifications are so arbitrary; and whenever I read a book with a road map, I have difficulty keeping track of the sections I should read and those I should skip.

One day while I was discussing my dilemma with Malcolm Haines¹ from London, he came up with a solution. Malcolm, who is one of the most creative people in IBM, suggested I mark the more difficult sections and let the reader decide whether or not to read it. He further suggested using chili peppers to denote the degree of difficulty of a particular section. This idea came from the fact that last year, Malcolm introduced me to an Anglo-Indian restaurant in London named Chutney Mary. This fine restaurant uses small drawings of red chili peppers in its menu to show which dishes are hot

<sup>&</sup>lt;sup>1</sup> Malcolm Haines is frequently referred to as IBM UK's "propaganda minister," whose duties include promoting IBM via videos and on commercial satellite television networks. Malcolm's AS/400 video, "The World's Greatest Architecture," is classic British humor.

— the more peppers, the hotter the seasoning. So, he reasoned, why not use the same approach to identify the "hotter" technical sections in this book?

My chili pepper rating system is as follows:

No chili peppers means the section is relatively mild when it comes to technical content; there will be some, but everyone needs a little spice.

One chili pepper means there is a little more technical detail. It is usually okay for most readers, but if it gets too hot, skip to a milder section.

Two chili peppers means the material is definitely beginning to pick up the technical content. You may want to try just a taste.

Bit-heads are beginning to smile, and sweat may break out on their foreheads when three chili peppers appear. The rest of us may find smoke coming out our ears if we concentrate too hard in these sections. Depending on your tastes, you may want to skip that section altogether.

Happy dining.

#### Chapter 1

# Advanced Application Architecture

The only certainty in computers is change. Technology is changing at such an astonishing rate that last year seems like part of ancient history. This is especially true in the PC world, where the hardware is practically obsolete before you get it out of the store. Hardware technology is as discardable as yesterday's newspaper.

The staying power of any computer system and its ability to protect the investment of its customers is the most important consideration in the purchase of a business computer. Over the years, AS/400 customers have heard about the AS/400's advanced architecture and how new technologies are incorporated into this system in a way that won't have a direct impact on them. They have been told that the architecture is *technology independent*, and that it is this characteristic that protects their investment. While it is true they have not had to change their application programs to take advantage of the new technologies, they often have not really understood — or cared about — how the system worked, as long as it worked.

With IBM's Advanced Series, the AS/400 architecture has once again come into the spotlight. New models incorporate a type of processor architecture called a *reduced instruction set computer* (RISC). For comparison, the processors used in the original AS/400, along with other popular processors such as the Intel Pentium and the Intel P6, are known as *complex instruction set computers* (CISC).

RISC processors generally have simpler instructions than CISC processors, which means that very high-speed processors can be built at reasonable cost. This improvement in cost/performance is an important reason to move to a RISC architecture, but there can be a downside.

For example, other computer vendors moved from CISC to RISC processors, and this move caused disruptions among some of their customers and independent software vendors (ISVs) who wrote application programs. Some application programs or parts of application programs had to be rewritten to move to the new hardware. This happened, for example, when Hewlett Packard (HP) introduced its Precision Architecture (PA) and when Digital Equipment Corporation (Digital) introduced its Alpha architecture.

To appreciate the magnitude of this disruption, consider Digital's move to RISC. Digital estimated that moving its installed base to the Alpha architecture caused from 15 percent to 20 percent of the older VAX architecture applications to be rewritten. For any customer or ISV, application rewrites of this magnitude could be very costly.

In contrast, the AS/400's technology-independent architecture protects the system's customers and ISVs from such disruptions as they move to the new RISC processors. To see how this is possible requires a look at how the AS/400's advanced application architecture differs from all others.

#### **Computer Architecture**

A Roman architect in the first century, Vitruvius, defined architecture as the act of designing a structure that had utility, strength, and the power to delight. The architecture of buildings and computers have this, and much more, in common.

Contemporary architecture owes much to the formal orders of classic architecture. Even the most futuristic designs spring from the past. The Egyptian pyramids, the Greek columns, the Roman arch, the Romanesque dome, and the Gothic pointed arch all furnish the foundation for creations we perceive today as the latest thing. In the history of computers, the ancient era starts only a few decades ago. As in building design, the most dynamic and exciting things happening today in computer architecture spring from discoveries and lessons learned from the "classics."

The AS/400 architecture is based on a model developed more than a quarter of a century ago. Because of a flexible design approach at the outset, the AS/400 has been able to adapt quickly and dynamically to modern goals and needs. With its technology-independent architecture, the AS/400 has had, for years, features and capabilities other computer systems still haven't achieved.

#### A Programmer's View

In 1970, S. S. Husson¹ defined computer architecture as "the attributes of the (computer) system as seen by the programmer." The architecture includes the set of instructions, data types, input/output (I/O) operations, and other features of the computer. We sometimes separate these and talk about instruction set architectures or I/O architectures. The total architecture

1 S. S. Husson, "Microprogramming Principles and Practices," Prentice-Hall, 1970. includes everything a programmer needs to know to make a program work correctly.

From a hardware perspective, a computer has five main components: input, output, memory, datapath, and control. The last two components are often combined and called the processor. The computer architecture defines what operations can be performed by these components. The processor gets instructions and data from the memory. Input hardware writes data to memory, and output hardware reads data from memory. The control hardware provides the signals to cause the operations of the datapath, memory, input, and output.

The processor is sometimes called the CPU, for central processing unit. The CPU name is being used less frequently these days because modern hardware technologies allow us to package entire processors on a single semiconductor chip. Many people use the terms CPU, processor, and processor chip interchangeably. We should, however, keep in mind that not all processors fit onto a single chip. A single processor may require a multichip implementation.

. If two computers can execute the same instruction set, they are said to have the same instruction set architecture. There can be, and usually are, multiple implementations of a given architecture. Thus, the Intel x86<sup>2</sup> architecture used in many PCs applies to a family of processor chips. These processor chips are realized in different technologies and running at different speeds. The important point here is that the specific technology used to build the computer is not a part of the architecture.

#### **Levels of Abstraction**

Most modern computers have hardware and software structures that contain several levels. Lower-level details are hidden to offer simpler models at the higher levels. This principle of abstraction is the way hardware and software designers deal with the complexities of computers.

At the lowest level, the electronic circuit, a computer is very simple. The electronic circuit only understands two commands: on and off. The symbols we use for these commands are the numbers 1 and 0. We communicate with the machine at this level with a string of 1s and 0s. An instruction is a collection of these binary digits, or bits, that the computer understands. An instruction is, therefore, nothing more than a number in the base 2 number system, or a binary number. We call computers digital computers because the machine language uses numbers for both instructions and data.

In the early days, programmers communicated with computers using binary numbers. This was not very efficient, so a higher level of abstraction, called the assembly language, was invented. The assembly language is a symbolic form for the binary machine language of the computer. An assembler is a program that translates the symbolic form of the instruction into the binary form.

<sup>2</sup> The Intel x86 CISC architecture is used in the family of single-chip processors that includes the 086, 186, 286, 386, 486, Pentium, and P6.

Assembly-level programming was still not a very natural notation for most programmers, so an even higher level of abstraction, called a *high-level programming language*, was created. There are hundreds of these languages today; a few of the better known ones are BASIC, C, COBOL, RPG, FORTRAN, and Pascal. The program that accepts one of these high-level programming languages and translates it into assembly language statements is called a *compiler*.

Writing a program in a high-level language (HLL) illustrates how multiple levels of software abstraction work in a computer. The compiler handles the mapping between the high-level language program and the assembly language level. The assembler then translates the assembly language instructions down to the binary machine level that the processor understands. Note that some compilers generate the binary machine language directly, eliminating the assembly level.

The compiler and assembler programs translate the high-level language program into machine language instructions prior to execution. This is a one-time operation, and unless the program is changed, repeating these steps is not necessary to rerun the program. Again, the reason for using these levels is to hide the details of the underlying binary machine language from the programmer to provide a simpler, more productive interface.

The same concept of multiple levels for software can also be true for hardware. Many processors, such as the Intel family, use an implementation technique called *microprogramming*. In a microprogrammed machine, an even lower-level instruction set is used to implement the binary machine language. Instead of using a compiler to map from the higher level to the lower level, microprogramming uses *emulation*. With emulation, machine instructions are fetched and executed one at a time using sequences of the lower-level instructions. There is no separate compile step required to transform the machine instructions into a form acceptable to the microprogram.

Emulation is similar to a software technique known as *interpretation*. Here a program, the interpreter, takes one instruction at a time and executes a sequence of equivalent lower-level instructions. Some high-level languages, such as BASIC, are designed to be easy to interpret. Most computer command languages are also interpretively executed. Type "dir" on the DOS screen of a PC and you will see a listing of the contents in a directory on your PC. A command interpreter in DOS reads the command you typed after you press the Enter key and then executes the sequence of instructions in the computer needed to carry out your command. Most operating systems have such a command interpreter. In a microprogrammed machine, special hardware usually has been added to help the interpretation process. The microprogram is called an emulator to identify this hardware-assisted form of interpretation.

The instruction set architecture of a computer system is usually thought of as the interface between the hardware and the lowest-level software. At

the time of Husson's definition of computer architecture, much programming was still done without using high-level languages. A better definition of computer architecture today might be "the attributes of the system as seen by the compiler," because few programmers deal with binary machine language programs.

With multiple levels, it is more accurate to think about a computer having multiple architectures, although the binary instruction set architecture still plays the most important role in most computers. When someone talks about the ability of one computer to execute the programs of another computer with no changes, they often say that the first can execute the binaries of the second computer. They mean that the programs can be moved without even requiring a recompile. The binary machine language of one computer is contained in the other computer.

#### **Software Design**

Within a computer system, there are generally two types of software: system software and application software. Operating systems, assemblers, and compilers are examples of system software. Application software, on the other hand, is aimed at the end user of the system and is often uniquely tailored for a particular business.

In the past, it was argued that both the system programmer and the application programmer needed access to the lowest-level architecture. This access was usually accomplished through an assembler. There were many reasons for this argument. Precious little memory was available for most programs, the processors were slow and expensive, and the compilers for high-level languages were not very sophisticated. When you needed to get the last ounce of performance out of the machine, "real" programmers used assembly language.

Many believe that assembly-level programming is a relic of the past, something no longer used; but that's not true. Most operating systems in use today incorporate lots of assembler code. This is not only true for the older operating systems, those that have their roots in the 1960s or early 1970s, but also for newer ones. The PC operating systems are good examples. Microsoft's Windows 95 is written mostly in Intel assembler language.

The original PC processors had very limited resources. Memories had a maximum size of 64 kilobytes. One kilobyte is equal to 210, or 1024 bytes, where a byte is an 8-bit entity in memory used to store a character or digit. Memory was so expensive that the operating system could take no more than 4 kilobytes. The use of assembler language allowed programmers to squeeze the code into the smallest possible space. So much of the operating system was written in assembler that, even when memory sizes increased because of dropping technology costs, it was not practical to go back and rewrite the original code.

To illustrate this, consider a computer that contains eight registers. A register, which is part of the processor datapath, is a high-speed storage area where data and addresses can be kept temporarily while being used by the processor. Registers are generally used to improve the performance of a program. Assume further that each register is 16 bits wide and that the programmer may load and store the registers at will. The existence of these registers and their characteristics show through to the assembly-language programmer. Therefore, every program written at the assembler level for this computer will know about the eight registers and will be dependent on them being there.