# An Optimized Grounded Base Oscillator Design for VHF/UHF

*Phase noise in oscillators, along with frequency stability and efficiency, is an important parameter in oscillator design.*

The design of VHF/UHF oscillators has been described in many books and journals with most of the emphasis on frequency stability and to some smaller part on output/efficiency. Since the introduction of reliable phase noise measurements and the ability to predict/simulate the phase noise, the improvement of this important parameter with the help of CAD and analytic equations has gained more attention. The vast majority of early publications focused on designs using small signal approaches, which give non-reliable answers for output frequency, output power and phase noise. The purpose of this paper is to validate the large signal time domain approach using the grounded base oscillator rather than the Colpitts oscillator. The key contributions are: (1) to predict the phase noise correctly using the large signal time domain calculations (Bessel functions) and nonlinear CAD simulators and derive a set of algebraic equations for the noise calculations (many of the CAD tools give incorrect answers about the phase noise), and (2) to provide a set of empirical equations to guide the synthesis of such “optimized” oscillators. This novel design concept using a time domain approach provides both the best output power and the best phase noise.

To have a point of reference the traditional small signal approach is first used followed by the novel approach shown here to get the optimum design. Using a mix of linear equations and one large signal parameter ( $g_m$ ), the important noise parameters are calculated and validated. Finally, based on this, a very simple but powerfully scalable set of formulas for the oscillator synthesis is shown, that provides extremely good results. In addition to this, the design principle for fixed or narrowband oscillator discussed here also applies to the broadband VCO design. We have shown that this design methodology works over a multi-octave tuning range.

## Reference Circuit

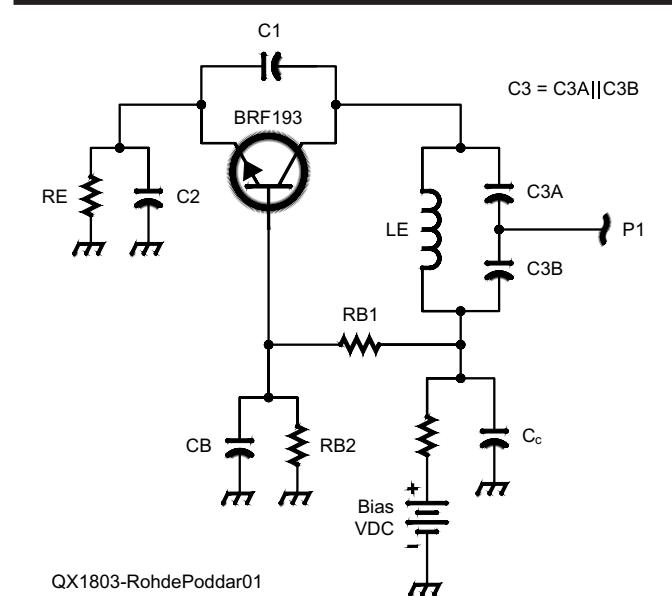

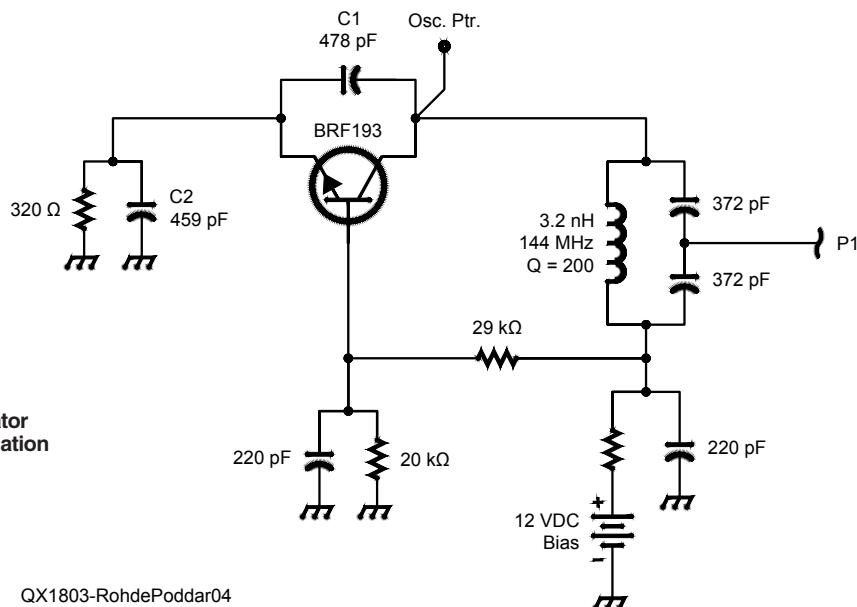

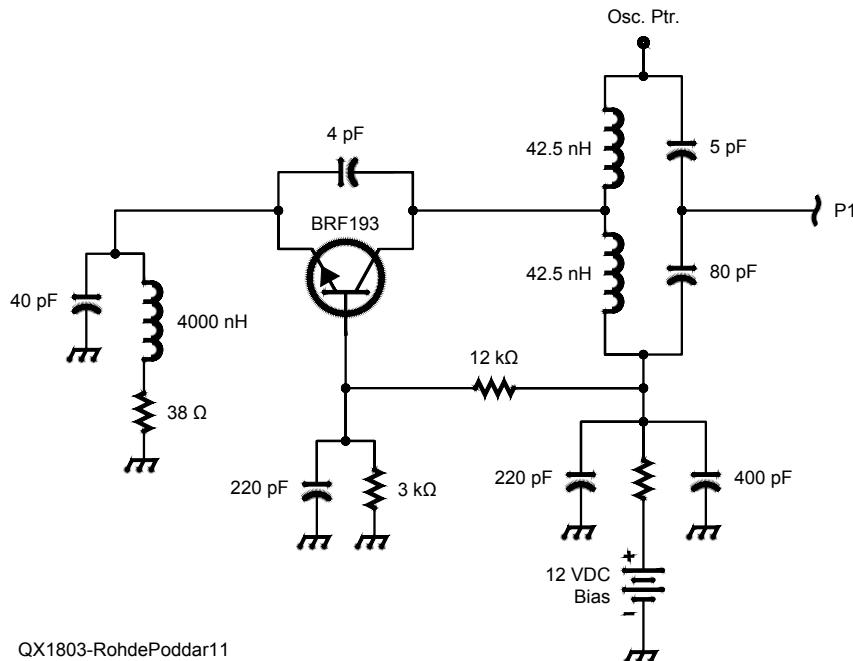

A very popular circuit for VHF/UHF oscillators is the grounded base configuration, which is shown in Figure 1. Its phase noise can be made very good, since the RF voltage swing at the collector can be close to the supply voltage. The circuit is simple and has been used for decades. The oscillator function is based on the principle that power from the output is taken and fed to the emitter. This feedback arrangement generates a negative resistance at the output, compensating the losses of the output-tuned circuit, and starts oscillating and then stabilizing the oscillation amplitude<sup>1-4</sup>. A

Figure 1—Typical configuration of grounded base oscillator circuit.

complete survey<sup>5–19</sup> of configurations and applications is referenced in the Notes. The design methodology works over a 3:1 frequency tuning range<sup>20–23</sup>.

Several books on the topic of oscillators have been published in the recent years, and the most popular ones are listed in the Notes. Many of the authors have attempted to predict the oscillator's performance based on a set of linear calculation including using the Leeson model [See Leeson<sup>24</sup>. — *Ed.*] or similar methods to determine the phase noise<sup>25,26</sup>. The problem is that there are important input parameters required, such as the large signal noise figure of the transistor, output power and operating Q. These are typically guessed, but not known. The first successful attempt to determine the large signal phase noise was by Rizzoli, et al.<sup>6</sup> and Annzil, et al.<sup>7</sup>.

But these approaches were not useful without a CAD tool and don't give any design guides. Another interesting phenomenon that

has been overlooked by the linear approach is that prediction of the exact oscillator frequency that can be far off compared to the actual frequency of oscillation.

The recent book by Gonzalez<sup>8</sup> gives an interesting overview of designing oscillators using linear calculations and CAD, but his design does not provide the optimum solution. To demonstrate this we are going to first use his way to design a 144 MHz Oscillator. The resulting circuit neither gives the best output power nor the best phase noise and, at high frequencies, requires values for the capacitors, which cannot be easily realized because of parasitic effects. Figure 1 shows the typical configuration of the grounded base oscillator circuit.

This oscillator type works well from RF frequencies like 10 MHz to above 1000 MHz. We will now follow the method of Gonzalez. For large signal conditions see Clarke<sup>11</sup>. Kenneth Clarke was probably the first to publish the effect of the collector current conducting angle of an oscillator, but makes no mentioning of the relationship of it on the phase noise, which is done by Johnson<sup>10</sup>.

### The [Y] parameters

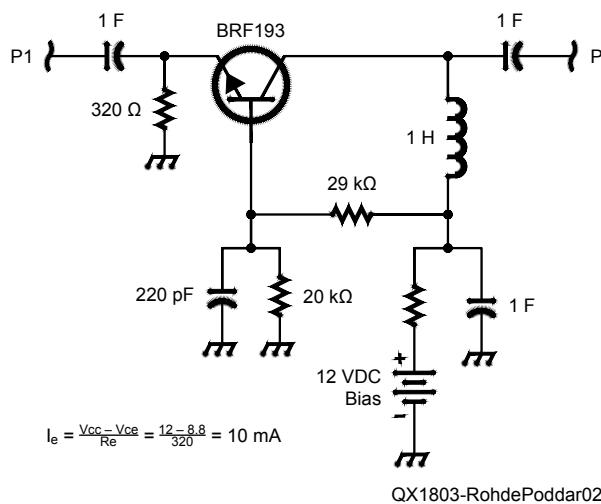

The first step is to determine the small signal [Y] parameters for the transistor BFR 193 (Infineon), at the frequency of 144MHz, and the operating point:  $I_c = 10 \text{ mA}$ ,  $I_B = 24 \mu\text{A}$ ,  $V_{be} = 0.64\text{V}$ ,  $V_{ce} = 8.8 \text{ V}$

Figure 2 — Small signal Y parameter generating circuit with CAD using Infineon time domain model

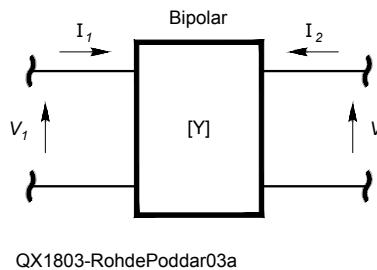

Figure 3(a) — Y-parameters based this definition.

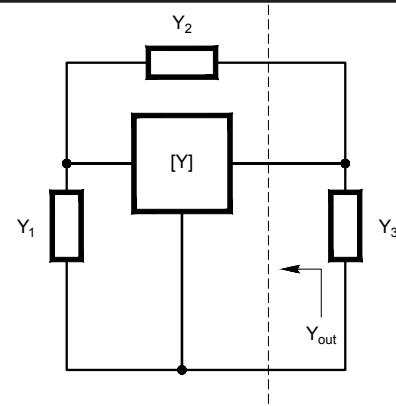

Figure 3(b) — Parallel feedback oscillator topology.

The 10 mA operating point was selected for a stable transistor cut-off frequency  $f_T$ . For more output power 30 mA is a better choice.

Figure 2 shows the circuit generating the small signal [Y] parameters using the Ansoft Designer CAD and the time domain model.

The CAD software generates the Y-parameters based on the following definition in Figure 3(a).

$$\begin{bmatrix} I_1 \\ I_2 \end{bmatrix} = \begin{bmatrix} Y_{11} & Y_{12} \\ Y_{21} & Y_{22} \end{bmatrix} \begin{bmatrix} V_1 \\ V_2 \end{bmatrix}$$

We obtain:

$$Y_{11} = G_{11} + jB_{11} = (279.08 - j95.07) \text{ mS}$$

$$Y_{21} = G_{21} + jB_{21} = (-271.32 + j100.77) \text{ mS}$$

$$Y_{12} = G_{12} + jB_{12} = (-1030 + j78.06) \mu\text{S}$$

$$Y_{22} = G_{22} + jB_{22} = (1020 + j536.14) \mu\text{S}$$

### Parallel Feedback Oscillator Topology

The feedback arrangement shown in Figure 3(b) is the standard feedback Oscillator topology using parallel elements. Theoretically the grounded base configuration can be rotated to be the Colpitts circuit. This statement is often found in the literature, see Kotzebue and Parrish<sup>5</sup>. It is based on the black box theory. If we look at the performance, it is not correct that a mathematical rotation yields the same performance. In the case of the Colpitts Oscillator the RF voltage swing is now limited by the base emitter and emitter to ground voltage and as a result there is less energy stored in the circuit and because of loading the operational  $Q$  can be less than in the grounded base configuration. Here  $V_{cb}$  is about 12 V. Also  $Y_{22cb}$  is less than  $Y_{22ce}$ , resulting less loading. The Colpitts oscillator is popular because of its simplicity, and its perceived high isolation as the output power is taken at the collector. However, due to the strong Miller effect at very high frequencies, this is not a true statement. These comments set aside the general approach in the time domain shown here is valid not only for the Colpitts Oscillator but other derivatives.

The necessary oscillation condition for the parallel feedback oscillators as shown in Figure 3(b) can be described by

$$Y_{out} + Y_3 \Rightarrow 0$$

This condition can be expressed as

$$\text{Det} \begin{bmatrix} Y_{11} + Y_1 + Y_2 & Y_{12} - Y_2 \\ Y_{21} - Y_2 & Y_{22} + Y_2 + Y_3 \end{bmatrix} = 0$$

$$Y_3 = -[Y_{22} + Y_2] + \frac{[Y_{12} - Y_2][Y_{21} - Y_2]}{[Y_{11} + Y_1 + Y_2]}$$

where  $Y_{ij}$  ( $i, j = 1, 2$ ) are the small signal  $[Y]$  parameters of the bipolar or FET model.

#### Calculation of the feedback network values [linear case]

As shown in Figure 3(b), the active 2-port network, together with the feedback elements  $Y_1$  and  $Y_2$ , are considered as a one-port negative resistance oscillator circuit. The following is an example of an oscillator design using the small signal parameter determined above at 8.8 V and 10 mA at 144 MHz. The output admittance  $Y_{out}$  is

$$Y_{out} = -Y_3$$

$$\Rightarrow [Y_{22} + Y_2] - \frac{[Y_{12} - Y_2][Y_{21} - Y_2]}{[Y_{11} + Y_1 + Y_2]}$$

The optimum values of feedback element are calculated from the expression of  $B_1^*$  and  $B_2^*$ , and for 10 mA are:

$$B_1^* = - \left\{ B_{11} + \left[ \frac{B_{12} + B_{21}}{2} \right] + \left[ \frac{G_{21} - G_{12}}{B_{21} - B_{12}} \right] \left[ \frac{G_{12} + G_{21}}{2} + G_{11} \right] \right\}$$

$$jB_1^* = j\omega C_1$$

$$C_1 \approx 478 \text{ pF}$$

$$B_2^* \approx 417 \times 10^{-3}$$

$$jB_2^* = j\omega C_2$$

$$C_2 \approx 459 \text{ pF}$$

The optimum values of the real and imaginary part of the output admittance are

$$Y_{out}^* = [G_{out}^* + jB_{out}^*]$$

where

$G_{out}^*$  and  $B_{out}^*$  are values for conjugate matching.

$$G_{out}^* = G_{22} - \left[ \frac{(G_{12} + G_{21})^2 + (B_{21} - B_{12})^2}{4G_{11}} \right]$$

$$\approx -74.5 \times 10^{-3}$$

needed to compensate the resonator losses ,

$$B_{out}^* = B_{22} + \left[ \frac{G_{21} - G_{12}}{B_{21} - B_{12}} \right] \left[ \frac{(G_{12} + G_{21})}{2} + G_{22} - G_{out}^* \right]$$

$$+ \left[ \frac{B_{21} + B_{12}}{2} \right]$$

$$\approx 214.74 \times 10^{-3}$$

$$C_3 \approx 237 \text{ pF}$$

$$\omega_0 = \frac{1}{2\pi\sqrt{LC}}; \quad C \approx 471 \text{ pF}$$

$$\text{For } f_0 = 144 \text{ MHz, } L_3 \approx 2.59 \text{ nH}$$

Figure 4 shows the 144MHz oscillator circuit using the small signal  $Y$  parameter for establishing oscillation conditions. The required values for this parallel feedback topology are: 478 pF for the feedback capacitor, 459 pF for the emitter to ground, the inductor 3.2 nH, and 186 pF for  $C_{3A}$  and  $C_{3B}$ . The bypass capacitors  $C_b$  and  $C_c$  should be about 220 pF.

However, it is practically impossible to manufacture capacitors above 200 pF to be capacitive at these frequencies. The best but awkward method then is to use a few capacitors in parallel.

Figure 4 — 144 MHz oscillator reference circuit for the evaluation of the linear approach.

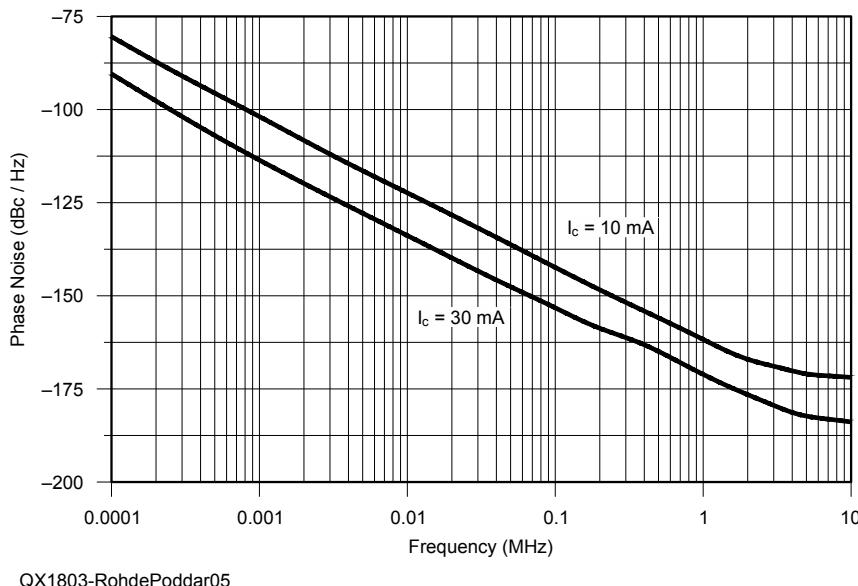

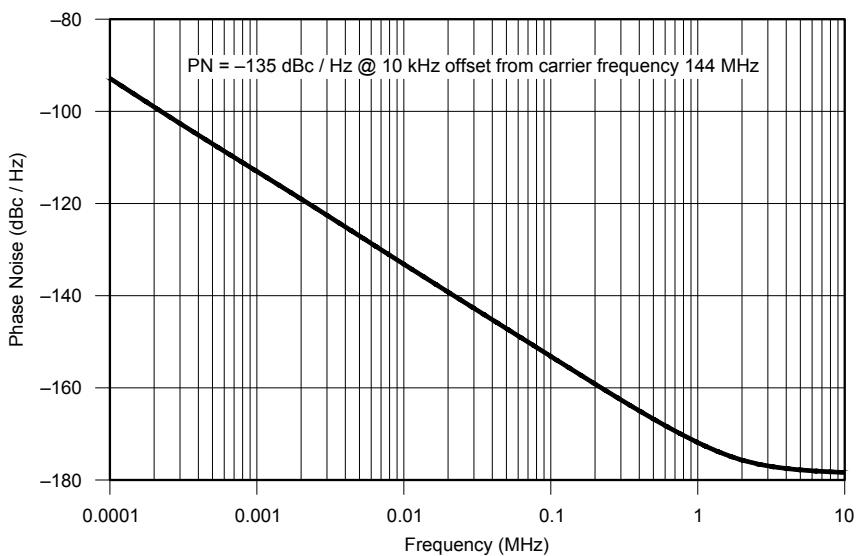

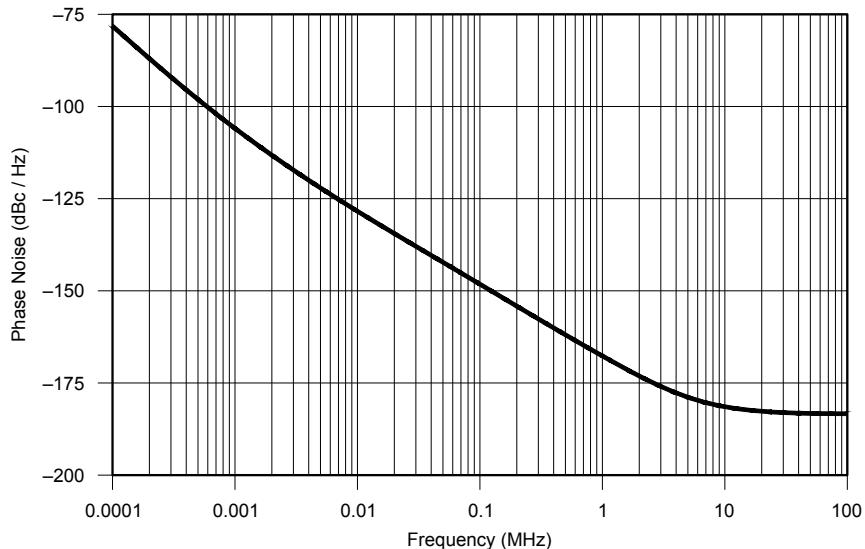

**Figure 5 — Phase noise plot of 144 MHz oscillator reference circuit for the evaluation of the linear approach (both 10 mA and 30 mA cases). The 30 mA case gives 10 dB lower phase noise than the 10 mA case.**

For 30 mA,

$$Y_{11} = G_{11} + jB_{11} = (437 - j295) \text{ mS}$$

$$Y_{21} = G_{21} + jB_{21} = (-427 + j296) \text{ mS}$$

$$Y_{12} = G_{12} + jB_{12} = (-1670 + j757) \text{ } \mu\text{S}$$

$$Y_{22} = G_{22} + jB_{22} = (1650 - j146) \text{ } \mu\text{S}$$

For  $f_0 = 144 \text{ MHz}$  and 30 mA, the component values are  $L = 3.77 \text{ nH}$ ,  $C_1 = 518 \text{ pF}$ ,  $C_2 = 503 \text{ pF}$ ,  $C_3 = 69 \text{ pF}$ ,  $C = 324 \text{ pF}$ , needless to say  $C_1$  and  $C_2$  are paralleled capacitors in the vicinity of 100 pF each.

Figure 5 shows the simulated plot of the phase noise. The “linear” calculation indicates a resonant frequency of 143.2 MHz, while the non-linear harmonic balance (HB) analysis supplies the correct frequency of 144.2 MHz (quite a difference in percent) and an output power of just 5.1 dBm, as seen in Figure 6. This value is determined using the HB programs Ansoft Designer (Nexxim). ADS gives the same answer. These CAD tools deviate less than 1 dB from measured results, if the input Spice type parameters for the transistor are accurate.

#### Large signal and noise analysis

There were a variety of efforts made to deal with the large signal conditions, like the time domain approach. Equation (10) in Johnson<sup>10</sup> is a first successful attempt to deal with the calculations of the output power with reasonable effort. There are many problems associated with both the large signal analysis as well as the noise analysis. From an experimental point of view it is virtually impossible to build all possible variations. So we were trying to determine if the Ansoft Designer, whose large signal noise analysis development we were involved with, would give us the correct prediction. We were aware that all researchers would primarily look for measured data (which we will show) and yet we had to convince them that our CAD tool

**Figure 6 — RF output power of 144 MHz oscillator reference circuit for the evaluation of the linear approach Both 10 mA (solid) and 30 mA (dashed) are shown. For 30 mA, 12dB more power is available, now a total of approximately 18 dBm.**

was reliable. Therefore we took a few critical circuits, running from crystal oscillators to VCOs and evaluated them again. These were available during the development of the Designer CAD tool, and we re-measured them, with more refined test equipment like the R&S FSUP 26 and its necessary options. We have shown<sup>12, 13</sup> that the accuracy of the prediction was within 0.5 dB of the measured results. During this effort to analyze the noise in oscillators with a set of equations using a minimum of expensive CAD tools, we found this was possible. These equations<sup>9</sup> will be used here.

#### A Novel Approach using the time-domain analysis for obtaining the best phase noise and output power.

The hunt for a combined low phase noise can be followed through the literature. Designers have published recipes, like the

use of low noise transistors, high Q circuit, and other things, but the consequences of the large signal operation and the resulting phase noise had not been fully understood. A complete mathematical treatment follows for a 144 MHz oscillator.

### Design steps

Step 1 — Calculation of the output power for the selected dc operating conditions.

We select the same circuit as above, and set  $f_0 = 144$  MHz.

The RF output current is:

$$\begin{aligned} I_{RF}(t) &= I_c(t) \cong I_e(t) \\ &= I_{dc} \left[ 1 + 2 \sum_1^{\infty} \frac{I_n(x)}{I_0(x)} \cos(n\omega t) \right] \\ &= 10 \times 10^{-3} [1 + 6.6]_{x=15} \\ &\Rightarrow I_{RF}(t) = 60 \text{ mA peak amplitude} \end{aligned}$$

where  $x$  is normalized drive level

$$x = \frac{qV_1}{kT}; V_1 = \text{Drive signal}$$

Considering 50  $\Omega$  load, the RF output power is calculated:

$$\begin{aligned} V_{RF}(f_0) &= I_{RF} \times 50 \\ &= 60 \times 10^{-3} \times 50 \\ &= 3 \text{ V peak amplitude} \end{aligned}$$

No  $V_{ce}$  saturation assumed.

The oscillator output power at 144 MHz is then

$$\begin{aligned} P_{out}(f_0) &= \frac{V_{RF}^2(f_0)}{2R_L} \\ &= \frac{9}{2 \times 50} = 90 \text{ mW} = 19.5 \text{ dBm} \end{aligned}$$

Step 2 — Calculation of the large signal transconductance for the normalized drive level  $x = 15$

$$\begin{aligned} Y_{21} \Big|_{\text{small signal}} &= \frac{I_{dc}}{kT/q} = \frac{I_{dc}}{V_T} = g_m \\ &\Rightarrow g_m = \frac{3 \times 10^{-3}}{26 \text{ mV}} \approx 115 \text{ mS} \end{aligned}$$

where  $k$  is the Boltzmann constant, and  $T = 298$  K.

The large signal transconductance  $G_m$  is now

$$\begin{aligned} Y_{21} \Big|_{\text{large-signal}} &= G_m(x) = \frac{qI_{dc}}{kTx} \left[ \frac{2I(x)}{I(x)} \right] \\ &\quad - \left[ \frac{2I(x)}{I(x)} \right] \\ &\approx 20 \text{ mS} \text{ (for } x \approx 15) \end{aligned}$$

This assumes an ideal intrinsic transistor. To perform the transition from the intrinsic to extrinsic transistor, we add the parasitics (package effects, lead inductance and bond wires) by correcting the final results for capacitances and inductances. The  $f_i$  of the transistor used is high enough so a phase shift correction for  $g_m$  is not necessary at this frequencies (VHF).

The value of  $n$  can be in the range of  $n [n_1, n_2]$ , where  $n_1$  is 2 and  $n_2$  is 5 for a drive level  $x = 15$  (low phase noise performance).

Assume  $n = 5$ , the values of  $C_1$  and  $C_2$  can be calculated to be

$$\frac{C_2}{C_1 + C_2} = \frac{1}{n} \Rightarrow C_2 = \frac{C_1}{n-1}$$

$$C_2 = \frac{C_1}{n-1} = \frac{C_1}{4} \Rightarrow \frac{C_1}{C_2} = 4$$

The ratio of the capacitor  $C_1$  to  $C_2$  is 4.

Step 3 — Calculation of  $C_1$  and  $C_2$ .

The value of  $C_1$  is selected for proper loading, therefore

$$XC_1 > Y_{11} \approx C_1 > \frac{Y_{11}}{\omega}$$

$$\Rightarrow C_1 > \frac{Y_{21}}{\omega} \cong C_1 \geq \frac{2G_m(x)}{\omega}$$

$$\Rightarrow C_1 > \frac{2 \times 20 \times 10^{-3}}{2 \times \pi \times 144 \times 10^6} \approx 44 \text{ pF}$$

For  $C_1/C_2 = 4$ ,  $C_2 \approx 11 \text{ pF}$ .

Step 4 — Calculation of  $C_3$  and  $C_4$ .

For optimum phase noise and power output,

$$C_3 \geq 2C_2 \Rightarrow C_3 = 22 \text{ pF},$$

and the capacitive transformer tapping ratio  $m$  ( $C_3/C_4$ ) should be greater than 10, therefore the impedance transformation is greater than 100. For  $C_3 = 22 \text{ pF}$ ,  $C_4$  is 220 pF.

Step 5 — Calculation of  $L$ .

$$\omega_0 = \frac{1}{2\pi\sqrt{LC}};$$

$$C = C_T + C_3;$$

$$C_T = \frac{C_1 \times C_2}{C_1 + C_2} \Rightarrow C \approx 30 \text{ pF}$$

For  $f_0 = 144$  MHz,

$$L_3 = \frac{1}{(2\pi \times 144 \times 10^6)^2 \times 29 \times 10^{-12}} \approx 39 \text{ nH}$$

Step 6 — Calculation of the  $[L/C]$  ratio.

The energy stored across the resonator circuit for a given conduction angle and drive level is dependent on the characteristic impedance,

$$Z_0 = \sqrt{\frac{L(\text{nH})}{C(\text{pF})}} = \sqrt{1200}$$

For optimum phase noise and output power,  $Z$  should be greater than 3.

For example, the  $L/C$  ratio for a good approach is

$$\frac{L_3}{C_3} = \frac{39 \times 10^{-9}}{30 \times 10^{-10}} = 13 \Rightarrow p > 10$$

Validation — We now use the same test circuit and apply the “new” component values just calculated.

### Phase Noise Calculation

We have shown<sup>9</sup> the phase noise calculations for the Colpitts oscillator. These calculations can also be used to get the phase noise of this circuit. It agrees well with both measurements and simulations using the harmonic balance simulator Ansoft Designer (Nexxim).

The individual phase noise contribution can be described by

$$\begin{aligned} PN_{inr}(\omega_0 + \Delta\omega) &= \frac{4KT}{R_p} [NFT_{inr}(\omega_0)]^2 \\ &= \frac{4KT}{R_p} \left\{ \frac{1}{2} \left[ \frac{1}{2j\omega_0 C_{eff}} \right] \left[ \frac{\omega_0}{\Delta\omega} \right] \right\}^2 \end{aligned}$$

→ Phase noise contribution from the resonator tank.

$$\begin{aligned} PN_{vbn}(\omega_0 + \Delta\omega) &= 4KTr_b [NFT_{vbn}(\omega_0)]^2 \\ &= 4KTr_b \left\{ \frac{1}{2} \left[ \frac{C_1 + C_2}{C_2} \right] \left[ \frac{1}{2jQ} \right] \left[ \frac{\omega_0}{\Delta\omega} \right] \right\}^2 \end{aligned}$$

→ Phase noise contribution from the base resistance.

$$\begin{aligned} PN_{ibn}(\omega_0 + \Delta\omega) &= 2qI_b [NFT_{ibn}(\omega_0)]^2 \\ &= 2qI_b \left\{ \frac{1}{2} \left[ \frac{C_2}{C_1 + C_2} \right] \left[ \frac{1}{j\omega_0 QC_{eff}} \right] \left[ \frac{\omega_0}{\Delta\omega} \right] \right\}^2 \end{aligned}$$

→ Phase noise contribution from the base current.

$$\begin{aligned} PN_{ifn}(\omega_0 + \Delta\omega) &= \frac{K_f I_b^{AF}}{f_m} [NFT_{ifn}(\omega_0)]^2 \\ &= \frac{K_f I_b^{AF}}{f_m} \left\{ \frac{1}{2} \left[ \frac{C_2}{C_1 + C_2} \right] \left[ \frac{1}{j2\omega_0 QC_{eff}} \right] \left[ \frac{\omega_0}{\Delta\omega} \right] \right\}^2 \end{aligned}$$

→ Phase noise contribution from the flicker noise of the transistor.

$$\begin{aligned} PN_{icn}(\omega_0 + \Delta\omega) &= 2qI_c [NFT_{icn}(\omega_0)]^2 \\ &= 2qI_c \left\{ \frac{1}{2} \left[ \frac{C_1}{C_1 + C_2} \right] \left[ \frac{1}{2j\omega_0 QC_{eff}} \right] \left[ \frac{\omega_0}{\Delta\omega} \right] \right\}^2 \end{aligned}$$

→ Phase noise contribution from the collector current.

The total effect of all the four noise sources can be expressed as

$$\begin{aligned} PN(\omega_0 + \Delta\omega) &= [PN_{inr}(\omega_0 + \Delta\omega)] \\ &\quad + [PN_{vbn}(\omega_0 + \Delta\omega)] \\ &\quad + [PN_{ibn}(\omega_0 + \Delta\omega)] \\ &\quad + [PN_{icn}(\omega_0 + \Delta\omega)] \end{aligned}$$

where

$K_f$  = Flicker noise constant

$AF$  = Flicker noise exponent.

$$C_{eff} = C + \frac{C_1 C_2}{C_1 + C_2}$$

Note that the effect of the loading of the  $Q$  of the resonator is calculated by the noise transfer function multiplied with the noise sources.

The phase noise contribution from the different noise sources for the parallel tuned Colpitts oscillator circuit at  $\Delta f = 10$  kHz from the oscillator frequency  $f_0 = 144$  MHz will now be computed.

### Circuit parameters

Base resistance of transistor  $r_b = 6.14 \Omega$ .

Parallel loss resistance of the resonator  $R_p = 7056 \Omega$ .

$Q$  of the resonator = 200 ( $Q$  of the inductor at 144 MHz)

Resonator inductance = 39 nH

Resonator capacitance = 22 F

Collector current of the transistor  $I_c = 10$  mA

Base current of the transistor  $I_b = 85 \mu\text{A}$ .

Flicker noise exponent  $AF = 2$

Flicker noise constant  $K_f = 10^{-7}$

Feedback factor  $n = 5$ .

Phase noise at 10 kHz is

$$PN_{inr}(\omega_0 + 10 \text{ kHz}) \approx -134.2 \text{ dBc/Hz}$$

$$PN_{vbn}(\omega_0 + 10 \text{ kHz}) \approx -151 \text{ dBc/Hz}$$

$$PN_{(ibn+ifn)}(\omega_0 + 10 \text{ kHz}) \approx -169.6 \text{ dBc/Hz}$$

$$PN_{icn}(\omega_0 + 10 \text{ kHz}) \approx -150.6 \text{ dBc/Hz}$$

The total sum of all the four noise sources can be expressed as

$$\begin{aligned} PN(\omega_0 + \Delta\omega) &= [PN_{inr}(\omega_0 + \Delta\omega)] \\ &\quad + [PN_{vbn}(\omega_0 + \Delta\omega)] \\ &\quad + [PN_{ibn}(\omega_0 + \Delta\omega)] \\ &\quad + [PN_{icn}(\omega_0 + \Delta\omega)] \approx -134.1 \text{ dBc/Hz} \end{aligned}$$

Note that the noise contribution from the resonator at this offset is the same as the flicker noise contribution from the transistor. For low- $Q$  cases, this can be identified as the flicker corner frequency.

Phase noise at 100 Hz is

$$PN_{inr}(\omega_0 + 100 \text{ Hz}) \approx -94.2 \text{ dBc/Hz}$$

$$PN_{vbn}(\omega_0 + 100 \text{ Hz}) \approx -111 \text{ dBc/Hz}$$

$$PN_{(ibn+ifn)}(\omega_0 + 100 \text{ Hz}) \approx -124.1 \text{ dBc/Hz}$$

$$PN_{icn}(\omega_0 + 100 \text{ Hz}) \approx -110.6 \text{ dBc/Hz}$$

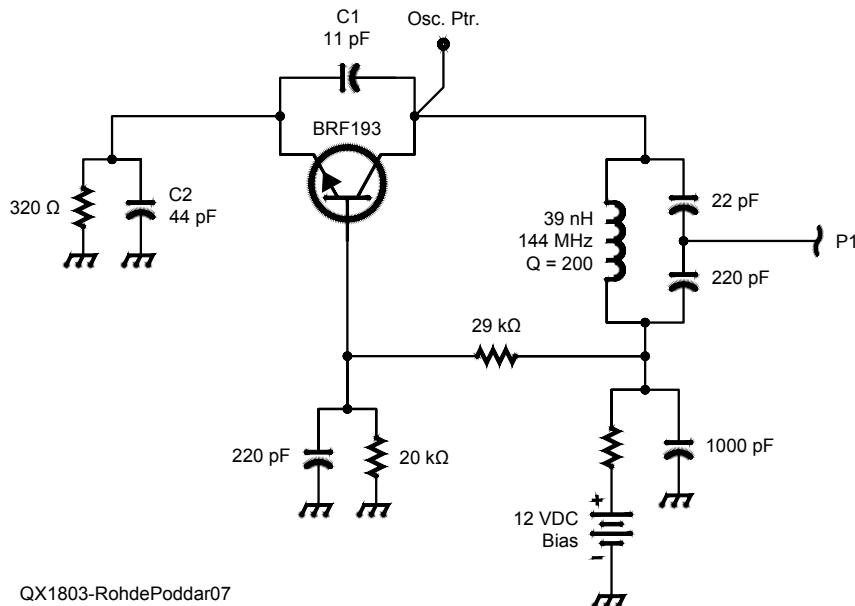

Figure 7 — 144 MHz oscillator reference circuit for the evaluation of the time domain approach.

The total sum of all the four noise sources can be expressed as

$$\begin{aligned}

PN(\omega_0 + \Delta\omega) = & [PN_{inr}(\omega_0 + \omega)] \\

& + [PN_{vbn}(\omega_0 + \omega)] \\

& + [PN_{ibn}(\omega_0 + \omega)] \\

& + [PN_{icn}(\omega_0 + \omega)] \\

\approx & -94.1 \text{ dBc/Hz}

\end{aligned}$$

It appears that the flicker noise and the noise from the resonator are the limiting factors for the overall phase noise performance of the oscillator circuit.

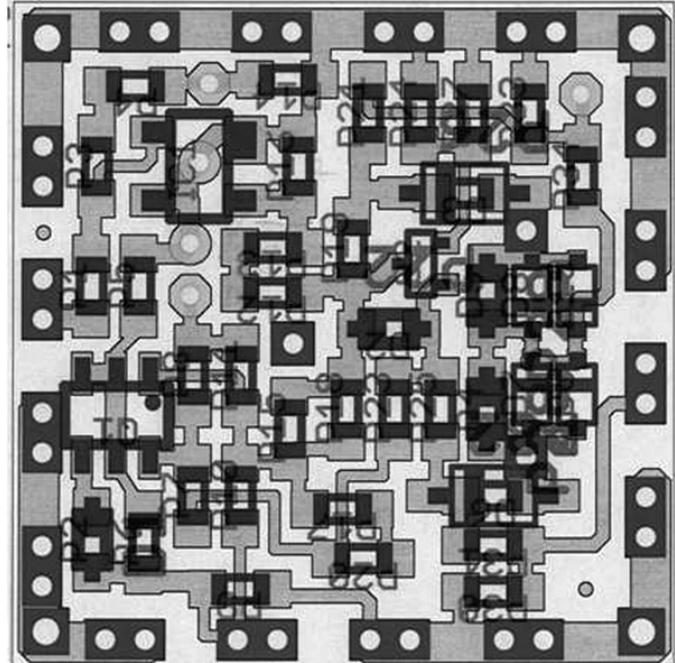

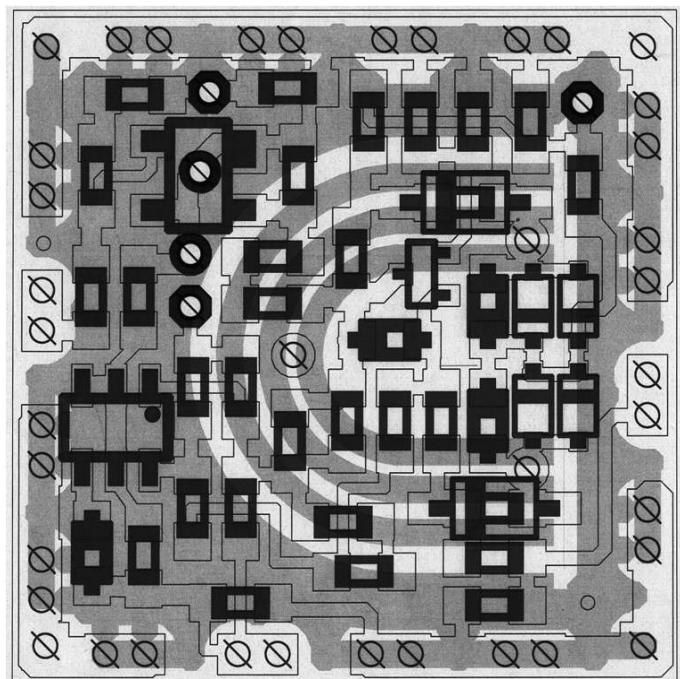

Figure 7 shows the schematic and Figure 8 shows the layout of the 144 MHz oscillator using time domain parameters at  $I_c = 10 \text{ mA}$ . The oscillator circuit shown in Figure 7 uses a lumped inductor of 39 nH and an unloaded Q of 200 at the operating frequency. Even at these frequency the layout is quite critical. The Figure 8 layout shows an assembly of component where the lead inductances have been kept small. The inductor is a standard off the shelf component.

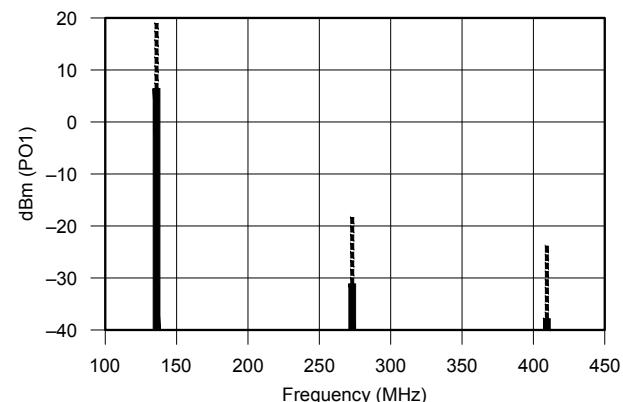

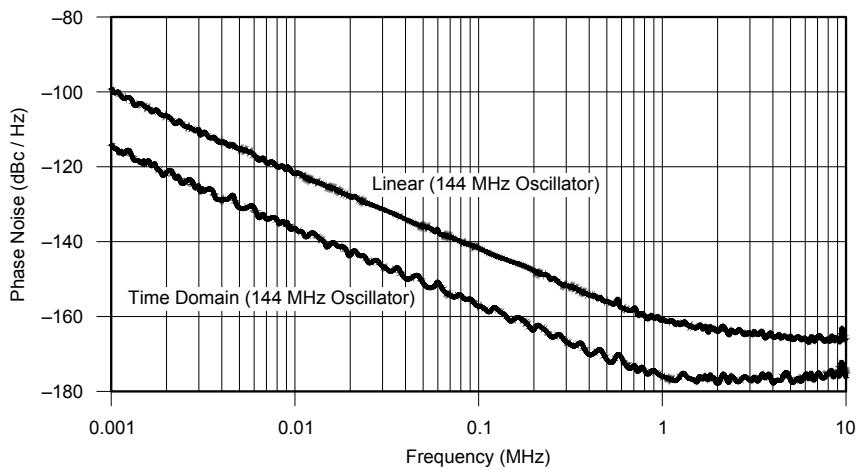

Figures 9 shows the CAD simulated phase noise plot, and Figure 10 shows the measured phase noise plot. The simulated and the validated output power now is 11.55 dBm (a 6 dB improvement compared to the linear case), and at 10 kHz offset from the carrier frequency the phase noise has been improved to be  $-135 \text{ dBc/Hz}$  from previously  $-122 \text{ dBc/Hz}$ , a 13 dB improvement. The outputs at the second and third harmonics are about -28 dBm and -34 dBm.

Using our phase noise calculation approach as shown above, the result is  $-134 \text{ dBc/Hz}$  and  $-94 \text{ dBc/Hz}$  at 10 kHz and 100 Hz offset. All three results, calculated, simulated, and measured result closely agrees within 1 dB. Many designers may not have access to CAD tools with oscillator noise calculation, and therefore this approach is extremely useful and cost saving.

If we now operate the same transistor at 30 mA, the phase noise at 10 kHz offset will be further improved to  $-144 \text{ dBc/Hz}$  and the output power is increased to 20 dBm. This shows that for low phase noise design a more powerful transistor is a good choice. It is important to

Figure 8 — Layout of 144 MHz oscillator circuit using LC lumped inductor capacitor resonator network

keep the dc dissipation of the device in mind, as the CAD approach does not flag a misuse of the device.

### Second Example: 433MHz oscillator circuit

We use the same transistor (BFR193) with,  $V_{ce} = 8.8 \text{ V}$ ,  $I_c = 10 \text{ mA}$ ,  $I_B = 85 \mu\text{A}$ ,  $V_{be} = 0.67 \text{ V}$ , and we now obtain:

$C_1 = 3.3 \text{ pF}$ ,  $C_2 = 13 \text{ pF}$ ,

$C_{3A} = 7.5 \text{ pF}$ ,  $C_{3B} = 75 \text{ pF}$ ,

$L_E = 13 \text{ nH}$ ,

$R_E = 320 \Omega$ ,  $R_{B1} = 29000 \Omega$ ,

$R_{B2} = 20000 \Omega$ ,

$C_B = 220 \text{ pF}$ ,  $C_c = 1000 \text{ pF}$ ,

$V_{dc} = 12 \text{ V}$

resulting an output power of 11.9 dBm and a phase noise of -100 dBc/Hz at 10 kHz offset from the carrier. Since the 144 MHz was about 35 dB better in the phase noise (-135 dBc/Hz at 10 kHz

offset), we need to ask why. The phase noise and the carrier frequency are related in a quadratic function. This means three times increase in frequency results in 9 dB degradation in phase noise for 432 MHz oscillator circuit in comparison to 144 MHz oscillator as shown in Figure 7. Therefore, phase noise performance for 432 MHz oscillator circuit should be -126 dBc/Hz instead of -100 dBc/Hz at 10 kHz offset (CAD simulated). The answer is that even in grounded base condition, large signal  $\text{Re}[Y_{22}]$  loads the parallel tuned circuit significantly resulting in a lower dynamic operating Q. We must find a work around for this.

The phase noise and the Q are related in a quadratic function. This means two times the Q results in 12 dB improvements. Since we lost 26 dB, we need to improve the dynamic loaded operating Q approximately 20 times. As this is not possible, there may be more

QX1803-RohdePoddar09

Figure 9 — Phase noise plot of 144 MHz oscillator reference circuit for the evaluation of the time domain approach.

Figure 10 — The measured phase noise plot for 144 MHz oscillator (linear and time domain).

Figure 11 — Schematic of 432 MHz grounded base oscillator using tapped inductor (30 mA).

effects than just the Q deterioration. The answer is, “the collector emitter capacitance dynamically detunes the circuit periodically”. A solution for this problem is tapping the inductor, therefore decreasing the influence of the transistor. We will show this now.

#### Modified Circuit for UHF (432 MHz) and Higher Current

If we inspect  $Y_{22}$  of our transistor at 432 MHz and at 30 mA, we will see that the loading of the tank circuit decreases the operating Q significantly. The way around this is to apply a center tapped inductor. As the coupling at these frequencies from winding to winding is not extremely high, actually two separate identical inductors can be used successfully.

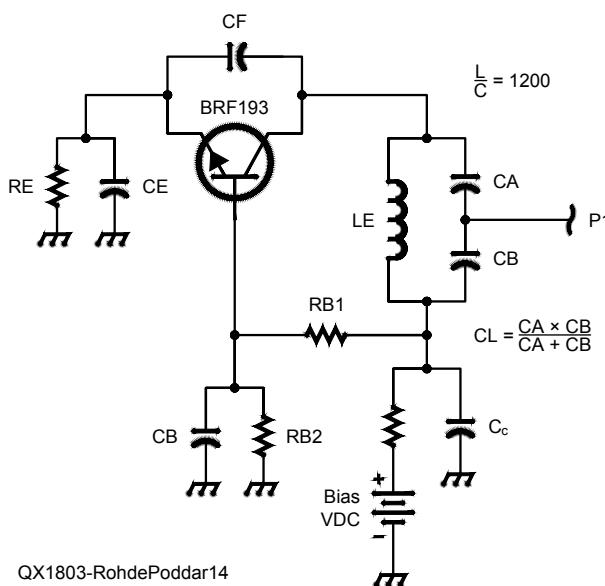

Figure 11 shows the schematic of a 432 MHz grounded base oscillator using the tapped inductor. This is a modification of the circuit we have used previously. In the case of a VCO, it would be advantageous to use a different output coupling scheme because in this configuration, the loading would vary with frequency. This can easily be achieved by adding some inductive coupling to the circuit. In case of a printed resonator this can be accomplished quite simply.

Figure 12 shows the layout of the 433 MHz oscillator circuit using buried printed coupled line resonator network (stripline resonator: middle layer). The actual resonator would not be visible if the oscillator is visually inspected.

Figure 13 shows the simulated phase noise plot. It shows the expected noise degradation of 9 dB, as the frequency is approximately three times higher. The resulting simulated output power at 432 MHz is 16 dBm, compared to 18 dBm at 144 MHz. This is due to internal package parasitics, which could not be compensated externally. The second harmonic is suppressed by 38 dB; this is due to the higher operating Q.

#### Circuit Design Guidelines

The results we have obtained so far were based on mathematical calculations. Some of these calculations are difficult to obtain. However, by inspecting the resulting circuits, there are certain

relationship between the values of the capacitance of the tuned circuit and the two feedback capacitors, the collector emitter capacitor and the emitter to ground capacitor. The following shows the set of recommended steps for easy design of such oscillator. Figure 14 shows the typical grounded base oscillator for demonstrating the simple design rules where  $C_E$  and  $C_F$  are the feedback capacitors that

Figure 12 — Layout of the 432 MHz oscillator circuit using buried printed couple line resonator network (stripline resonator in the middle layer).

QX1803-RohdePoddar13

Figure 13 — The simulated phase noise plot of 432 MHz grounded base oscillator using tapped inductors.

QX1803-RohdePoddar14

Figure 14 — Typical configuration of grounded base oscillator circuit.

generates the negative resistance to compensate the loss resistance of the resonator network comprised of  $L_E$  and  $C_L^*$ .

#### Simple Design Rules With an Example:

By setting the  $L/C$  ratio to a fixed value of 1200 (this is done for optimum energy storage, group delay and energy transfer for a given cycle in the resonator network), the following should be used.

$$\frac{1}{C} = \left[ \frac{1}{C} \right]_{\text{Grounded Base}} = 1200$$

$$\Rightarrow = \sqrt{1200} \approx 34.6 \Omega$$

$$L = 1200 \times C$$

$$\Rightarrow L_E = 1200 \times C_L^*$$

$$f = \frac{1}{2\pi\sqrt{LC}}$$

$$= \frac{1}{2\pi\sqrt{1200}}$$

$$C_L^* = C_L + \frac{C_E C_F}{C_E + C_F}$$

where  $C_E$  ( $C_1$ ) and  $C_F$  ( $C_2$ ) are feedback capacitors.

$$C_L = \frac{C_A C_B}{C_A + C_B};$$

where  $C_A$  ( $C_1$ ) and  $C_F$  ( $C_2$ ) are feedback capacitors.

$$C_B = 10 C_A.$$

To examine the accuracy of this simple approach, let us take the same 144 MHz grounded base oscillator as shown in Figure 7.

#### Example: The 144 MHz Grounded Base Oscillator

$$C_L^* = \frac{1}{2\pi f \sqrt{1200}} \Rightarrow C \approx 31 \text{ pF}$$

$$L_L = \frac{1}{(2\pi f)^2 C} \Rightarrow L \approx 39 \text{ nH}$$

$$C_F = 0.3 \times C_L^* \approx 11 \text{ pF}$$

$$C_L = 2 \times C_F \approx 22 \text{ pF}$$

$$C_E = 4 \times C_F \approx 44 \text{ pF}$$

$$C_A = 22 \text{ pF}$$

$$C_B = 220 \text{ pF}$$

These results are comparable with the results above and the calculation is frequency scalable with minor corrections possibly, if necessary. Other alternative short formulas based on linear approximations and published in the literature may not deliver the same high performance.

## Summary

Today's applications, both commercial and consumer, require low cost high performance oscillators and the design time is also very critical. The approach shown here meets these requirements and gives detailed guidelines for better performing oscillators. The concept is explained in detail and validated. This is only one of the many applications for which this technique is applicable. Furthermore, by translating this design to integrated circuits very high performance but very low cost oscillators can be made. From a theoretical point, we found it surprising that simple equations could be found which optimized the design and accurately predicted the phase noise. For the determination of the output power, a nonlinear CAD tool is recommended if the frequencies are higher than 500 MHz. Our example has shown that at frequencies below 200 MHz the output power can be determined quite accurately using this approach.

To make this oscillator part of a PLL synthesizer, electronic tuning is required. The output capacitor should then have a set of tuning diodes in parallel, with light coupling, to properly select the tuning range.

*Prof. Dr.-Ing. habil. Dr. h.c. mult. Ulrich L. Rohde, NIUL, is the Chairman of Synergy Microwave Corp., Paterson, NJ; President of Communications Consulting Corporation, serving as an honorary member of the Senate of the German Joint Forces University Munich; honorary member of the Senate of the Brandenburg University of Technology Cottbus-Senftenberg, Germany; past member of the Board of Directors of Ansoft Corporation, Pittsburgh, PA; and is a partner of Rohde & Schwarz, Munich, Germany. He presented numerous lectures worldwide regarding communications theory and digital frequency synthesizers. Dr. Rohde has published more than 300 scientific papers in professional journals and several books and book chapters, and several dozen patents. Dr. Rohde is a Fellow Member of the IEEE, Member of the IEEE Technical Committee for HF, VHF, and UHF Technology MTT-17, Member of the IEEE Signal Generation and Frequency Conversion MTT-22, Member of the Board of Trustees Fraunhofer Gesellschaft (EMFT) for Modular Solid State Technology, Member of the Board of Friends of the Bavarian Academy of Science and Humanity, and Honorary Member of the Academy of Science, all in Munich, Eta Kappa Nu Honor Society, Executive Association of the Graduate School of Business Columbia University, NY, the Armed Forces Communications & Electronics Association, Fellow of the Radio Club of America, former Chairman of the Electrical and Computer Engineering Advisory Board at New Jersey Institute of Technology, IFCS C. B. Sawyer Award recipient, IFCS I. I. Rabi Award recipient, Honorary Professor at IIT Delhi, India, Chief Judge of IEEE IMS 2014 Student Design Competition, and PhD Defense Committee Member at UCLA and Drexel University. His hobbies include sailing, US Merchant Marine Officer, Master of Steam or Motor Vessels, photography and licensed Amateur Radio operating since 1956 (DJ2LR and NIUL).*

*Dr. Ajay Poddar, AC2KG, is an IEEE Fellow, technological leader, and distinguished scientist. He graduated from IIT Delhi, India; Doctorate (Dr.-Ing.) from TU-Berlin, Germany; Post Doctorate (Dr.-Ing. habil) from Brandenburg Technology University, Cottbus, Germany. From 1990 until 2001 he has worked as Senior Scientist and Program Manager at Defense Research & Development Organization (DRDO) India. From 2001, he has been working as a Chief Scientist at Synergy Microwave, responsible for design and development of frequency generating and time keeping electronics, RF-MEMS based microwave/millimeter wave components, Negative Index inspired Metamaterial-Mobius resonators for sensors, and Optoelectronics for industrial, medical, and space applications. Dr. Poddar is a full professor at Oradea University, Romania and Guest lecturer at Technical University, Munich, Germany, and PhD advisor at several universities worldwide. He has received over dozen awards for scientific and technological innovations, over two dozen patents, authored/coauthored 6 technical books, and*

*published over 300 scientific papers in professional journals and conference proceedings. He is a recipient of IEEE 2015 IEEE IFCS W.G. Cady Award, 2015 IEEE RI Scientific innovation Award, and 2009 IEEE RI Scientific Contributions Award. Dr. Poddar has been actively involved for more than 30 years in charitable and volunteer service (Red Cross, Tsunami Relief, and Blind Community) for public causes.*

## Notes

- <sup>1</sup>F. E. Terman, *Radio Engineers Handbook*, pp. 498 ff, McGraw-Hill Inc, NY, 1943, ASIN: B000GWIWFM.

- <sup>2</sup>F. Langford-Smith, Editor, *Radiotron Designers Handbook*, pp. 947 ff., Electron Tube Div. RCA, Harrison, NJ, 1954, ASIN: B000JLVBH4.

- <sup>3</sup>L. J. Giacolotto, *Electronics Designers Handbook*, p. 16-1, McGraw Hill Book Company, Inc, NY, 1977.

- <sup>4</sup>F. Vilbig, *Lehrbuch der Hochfrequenztechnik*, Vol. 2, pp. 235, Akademische Verlagsgesellschaft Becker & Erler Kom.-Ges., 1937/1942, ISBN: 9780070231498.

- <sup>5</sup>K. L. Kotzubue and W. J. Parrish, "The use of large signal S-Parameters in microwave oscillator design," in *Proc. 1975 Int. Microwave Symp. On Circuits and Systems*.

- <sup>6</sup>V. Rizzoli, A. Neri, A. Costanzo, F. Mastri, "Modern Harmonic-Balance Techniques for Oscillator Analysis and Optimization," in *RF and Microwave Oscillator Design*, ed. M. Odyniec, Artech House, 2002.

- <sup>7</sup>W. Anzill, F.X. Kaertner, P. Russer, "Simulation of the Single-Sideband Phase Noise of Oscillators," *Second International Workshop of Integrated Nonlinear Microwave and Millimeterwave Circuits*, 1992.

- <sup>8</sup>G. Gonzalez, *Foundations of Oscillator Circuit Design*, Artech House, Inc., 2007, ISBN 10: 1-5963-162-0.

- <sup>9</sup>U. L. Rohde, A. K. Poddar, and G. Boeck, *The Design of Modern Microwave Oscillator for Wireless Applications Theory and Optimization*, ISBN 0-471-72342-8.

- <sup>10</sup>K. M. Johnson, "Large Signal GaAs MESFET Oscillator Design", *IEEE Trans. on MTT-27*, No. 3, Mar 1979.

- <sup>11</sup>K. K. Clarke, "Design of Self-Limiting Transistor Sine-Wave Oscillator", *IEEE Transaction on Circuit and Systems*, [legacy, pre-1988], vol. 13, Issue 1, Mar 1966, pp. 58-63.

- <sup>12</sup>U. L. Rohde and J. Whitaker, *Communication Receivers: DSP, Software Radios, and Design, Third Edition*, McGraw-Hill, pp.413-422, 2001, ISBN:0-07-136121-9.

- <sup>13</sup>U. L. Rohde and D. P. Newkirk, *RF/Microwave Circuit Design For Wireless Applications*, 2000, pp.798-812, 413- 422, ISBN:0-471-29818-2.

- <sup>14</sup>M. Gitterman, *The Noisy Oscillator The First Hundred Years, From Einstein Until Now*, World Scientific Publishing Co., 2005, ISBN 981-256-512-4.

- <sup>15</sup>M. Tiebout, *Low Power VCO Design in CMOS*, Springer Series in Advanced Microelectronics, Springer Berlin Heidelberg 2006, World Scientific, Singapore 596224, 2005, ISBN: 3-540-24324-0.

- <sup>16</sup>E. Camargo, *Design of FET Frequency Multipliers and Harmonic Oscillators*, Artech House, Inc, 1998, ISBN 0-89006-481-4.

- <sup>17</sup>R.I.W. Rhea, *Oscillator Design And Computer Simulation, Second Edition*, SciTech Publishing, 911 Paverstone Dr., Raleigh, NV 27615, 2006, ISBN: 1-884932-30-4.

- <sup>18</sup>M. Odyniec, Editor, *RF And Microwave Oscillator Design*, Artech House, Inc., 2002, ISBN 1-58053-320-5.

- <sup>19</sup>Peter Vizmuller, *RF Design Guide: Systems, Circuits and Equations*, Artech House, 1995, ISBN 0-89006-754-6.

- <sup>20</sup>U. L. Rohde and A. K. Poddar, "Impact of Device Scaling on Oscillator/VCO Phase Noise in SiGe HBTs," *International Semiconductor Device Research Symposium*, ISDRS 2005, USA, December 7-9, 2005.

- <sup>21</sup>U. L. Rohde and A. K. Poddar, "Reconfigurable Concurrent Oscillators For Multi-Band Multi-Mode Wireless Communication Systems", *IEEE Sarnoff Symposium*, Princeton, NJ, 30 April - 02 May 2007.

- <sup>22</sup>U. L. Rohde and A. K. Poddar, "Wideband voltage controlled oscillators employing evanescent mode coupled resonators," *US Patent 7,180,381*, Feb 2, 2007.

- <sup>23</sup>U. L. Rohde, A. K. Poddar, and R. Rebel, "Integrated Low Noise Microwave Wideband Push- Push VCO", *US Patent 7,088,189*, Aug 2006.

- <sup>24</sup>D. B. Leeson, "A Simple Model of Feedback Oscillator Noise Spectrum", *Proceedings of the IEEE*, Feb. 1966, 54 (2), pp. 329-330.

- <sup>25</sup>[www.microwavejournal.com/articles/29151-noise-analysis-then-and-today?v=preview](http://www.microwavejournal.com/articles/29151-noise-analysis-then-and-today?v=preview).

- <sup>26</sup>Ulrich L. Rohde and Anisha M. Apte, "Everything You Always Wanted to Know About Colpitts Oscillators", *IEEE Microwave Magazine*, Aug. 2016, pp. 59-76.