### **Contents**

- 8.1 Introduction to DSP

- 8.2 Introduction to SDR

- 8.2.1 SDR Architecture Options

- 8.2.2 Advantages and Limitations of DSP and SDR

- 8.3 Analog-Digital Conversion

- 8.3.1 Basic Conversion Metrics

- 8.3.2 Analog-to-Digital Converters

- 8.3.3 Analog-to-Digital Converter Subsystems

- 8.3.4 Digital-to-Analog Converters (DAC)

- 8.3.5 Choosing a Converter

- 8.4 Data Converters for SDR and DSP

- 8.4.1 Using Audio ADCs for SDR

- 8.4.2 High-Speed ADCs for SDR

- 8.5 Digital Signal Processors

- 8.5.1 Microprocessor-type DSP ICs

- 8.5.2 Fixed-Point versus Floating-Point

- 8.5.3 DSP in Embedded Systems

- 8.5.4 Typical DSP Processors

- 8.5.5 DSP Without a Dedicated Processor

- 8.5.6 Using Graphics Processors for DSP

- 8.6 Digital (Discrete-time) Signals

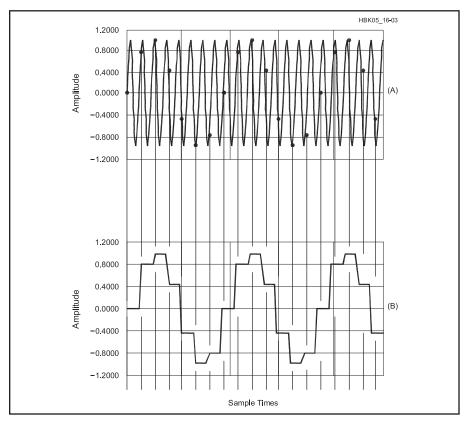

- 8.6.1 Sampling Digitization in Time

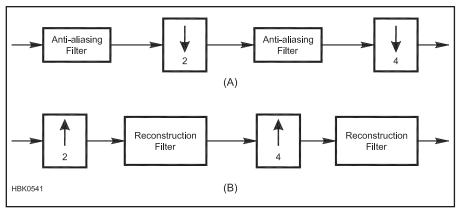

- 8.6.2 Decimation and Interpolation

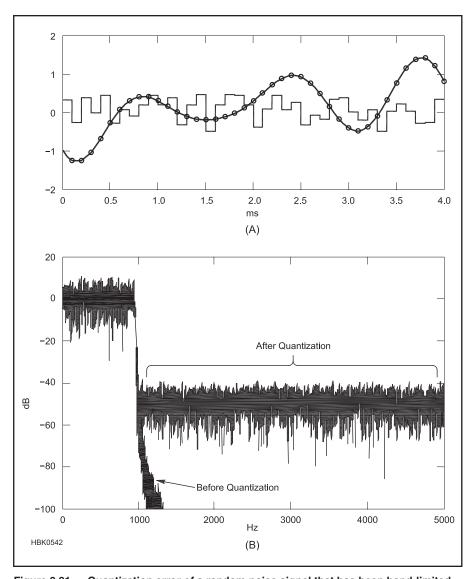

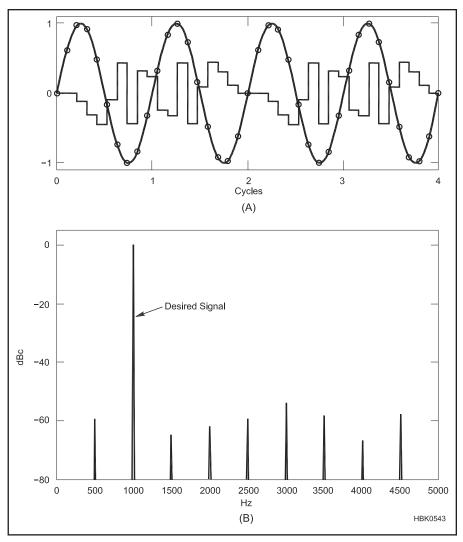

- 8.6.3 Quantization Digitization in Amplitude

- 8.7 The Fourier Transform

- 8.7.1 The Fast Fourier Transform (FFT)

- 8.7.2 Non-periodic Signals

- 8.7.3 The Inverse Fourier Transform (IFT)

- 8.8 References and Bibliography

### **Chapter 8 — Online Content**

- SDR Simplified Fourier Transforms by Ray Mack, W5IFS

- SDR Simplified Fundamentals of Sampling by Ray Mack, W5IFS

- SDR Simplified More on Sampling by Ray Mack, W5IFS

- "Radio Mathematics" see online content for the Electrical Fundamentals chapter

# Chapter **8**

# **DSP** and **SDR** Fundamentals

This chapter was updated by Doug Grant, K1DG, from material originally created by Alan Bloom, N1AL. It explores the fundamentals of digital signal processing (DSP) and software defined radio (SDR). Material is also taken from QEX "SDR: Simplified" articles by Ray Mack, W5IFS. Key to DSP and SDR, analog-digital conversion and types of converters are covered, as well.

DSP technology has progressed to the point where it is the dominant technology in our radio equipment. DSP has largely replaced analog hardware circuits with digital processors and software, offering amateurs flexibility and features only dreamed of in the past.

Software defined radio has displaced the superheterodyne architecture that was dominant since its introduction in the 1920s. SDR is only possible through DSP techniques implemented on the advanced platforms that have become available.

This chapter begins with the fundamentals of DSP and extends them to SDR design. Other chapters will cover DSP methods in more detail for implementing oscillators, modulation, filters, and the functions associated with receiving and transmitting.

For the fullest understanding of this chapter, the reader should have a basic familiarity of the topics covered in the Radio Fundamentals chapter as well as some high-school trigonometry.

References to math tutorials are provided in Radio Mathematics which is part of this book's online content along with additional background and support materials, including a glossary.

### 8.1 Introduction to DSP

Digital signal processing (DSP) has been around a long time. The essential theory was developed by mathematicians such as Newton, Gauss, and Fourier in the 17th, 18th, and 19th centuries. It was not until the latter half of the 20th century, however, that digital computers became available that could do the calculations fast enough to process signals in real time. Today DSP is important in many fields, such as seismology, acoustics, radar, medical imaging, nuclear engineering, audio and video processing, as well as voice and data communications.

In all those systems, the idea is to process a digitized signal so as to extract information from it or to control its characteristics in some way. For example, an EKG monitor in a hospital extracts the essential characteristics of the signal from the patient's heart for display on a screen. A digital communications receiver uses DSP to filter and demodulate the received RF signal before sending it to the speaker, headphones, or waterfall/band-scope display. In some systems, the signal to be processed may have more than one dimension. An example is image data, which requires two-dimensional processing. Similarly, the controller for an electrically-steerable antenna array uses multi-dimensional DSP techniques to determine the amplitude and phase of the RF signal in each of the antenna elements. A CT scanner analyzes X-ray data in three dimensions to determine the internal structures of a human body.

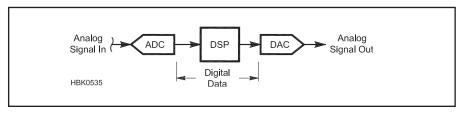

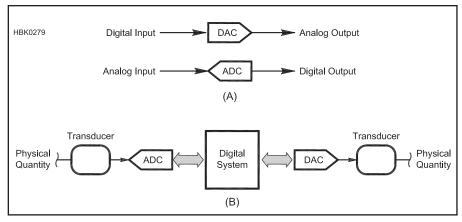

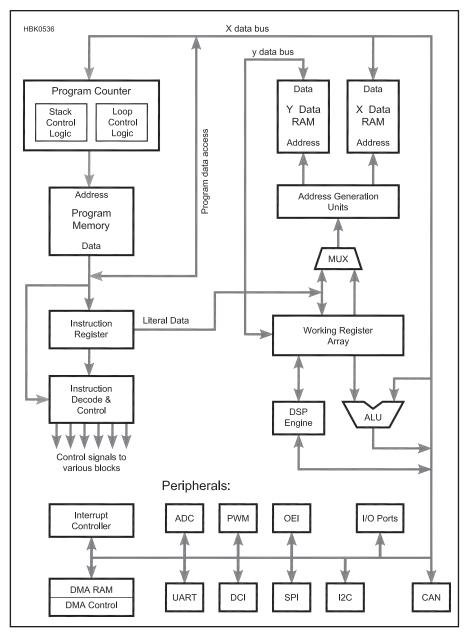

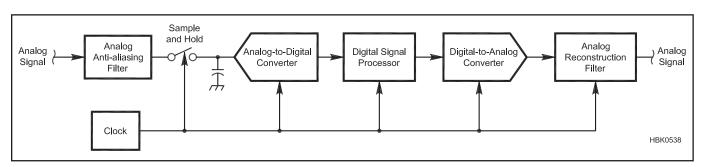

A typical DSP system is conceptually very simple. It consists of only three sections, as illustrated in Figure 8.1. An analog-to-digital converter (ADC, or A/D) at the input converts an analog signal into a series of digital numbers that represent snapshots of the signal at a series of equally spaced sample times. The digital signal processor does some kind of calculations on that digital signal to generate a new stream of numbers at its output. A digital-toanalog converter (DAC, or D/A) then converts those numbers back into analog form.

Some DSP systems may not have all three components. For example, a DSP-based audiofrequency generator does not need an ADC. Similarly, there is no need for a DAC in a measurement system that monitors some sensor output, processes the signal, and stores the result in a computer file or displays it on a digital readout.

The term "DSP" is normally understood to imply processing that occurs in real time, at least in some sense. For example, an RF or microwave signal analyzer might include a DSP coprocessor that processes chunks of sampled data in batch mode for display a fraction of a second later.

Figure 8.1 — A generic DSP system.

### 8.2 Introduction to SDR

The concept of a *software-defined radio* (SDR) has been around for a long time, but became popular in the 1990s. By then, DSP and data converter technology had developed to the point that it was possible to implement almost all the signal-processing functions of a transceiver using inexpensive programmable digital hardware. The frequency, bandwidth, modulation, filtering, and other characteristics can be changed under software control, rather than being fixed by the hardware design as in a conventional analog radio. Adding a new modulation type or a new improved filter design is a simple matter of downloading new software.

Compared to analog radios, SDR has some major advantages. In analog radios, passive components such as capacitors, resistors, and even inductors are subject to changes in value due to temperature drift and aging. They also have loose initial value tolerances and often require adjustments or calibration. Likewise, active components such as amplifiers and mixers also are subject to variations in performance. If the function of these components can be replaced with software, most of these problems disappear.

SDR is appealing to regulatory bodies such as the FCC because it makes possible a communications system called *cognitive radio* in which multiple radio services can share the same frequency spectrum.<sup>1</sup> Each node in a wireless network is programmed to dynamically change its transmission or reception characteristics to avoid interference to or from other users. In this way, services that in the past enjoyed fixed frequency allocations but that only use their channels a small percentage of the time can share their spectrum with other wireless users with minimal interference.

There has been much, sometimes heated, discussion about the precise definition of a software-defined radio (SDR). Most feel that, at minimum, an SDR must implement in software at least some of the functions that have traditionally been done in hardware. Others feel that a radio doesn't count as an SDR unless nearly all the signal-processing functions, from the RF input to the audio output (for the receiver) and from the microphone ADC (analog-to-digital converter, or A/D) to the power amplifier input (for the transmitter), are done in software. Others add the requirement that the software must be re-configurable by downloading new code, preferably open-source. For our purposes we will use a rather loose definition and consider any signal-processing function done in software to fall under the general category of SDR.

Some SDRs use a personal computer to do the computational work and external hardware to convert the transmitted and received RF signals to lower-frequency signals that the computer's audio interface can handle. Some SDRs avoid the use of the PC's sound card by including their own audio codec (short for "coder-decoder," a chip that includes both A/D and D/A converter functions) and using analog audio for the user interface. Some SDRs transfer the downconverted (and possibly filtered) data to the PC via a USB port. Modern PCs provide a lot of computational power for the money and are getting cheaper and more powerful all the time. They also come with a large color display, a keyboard and mouse for easy data entry and navigation, a large memory and hard disk, which allows running logging programs and other software while simultaneously doing the signal processing required by the SDR.

Smaller, even less expensive, computing platforms such as Arduino, Raspberry Pi, Beaglebone, Red Pitaya and many others have become available. While they often lack the peripherals and user interfaces of a complete PC, some of them have sufficient computational power to be useful for SDR experimentation.

Some SDRs have almost no knobs or buttons on the box and none of the traditional features such as frequency display, meters, and so on. In such radios, all control functions are done on an external PC with control software provided by the manufacturer. The user interface is the PC keyboard, monitor, and mouse. Other SDRs look more like conventional analog radios and don't need an external PC for control. While the signal processing is done with one or more embedded DSPs, the user interface consists of knobs and pushbuttons which many users prefer to a mouse and keyboard and pull-down menus. Some newer SDRs use a touchscreen for the user interface to emulate the buttons.

Either method offers all the important advantages of applying DSP techniques to signal processing. The channel filter can have a much better shape factor (the ratio between the width of the passband and the frequency difference of the stopband edges). FIR filters are linear phase and have less ringing than analog filters of the same bandwidth and shape factor. Once the signal is in the digital domain all the fancy digital signal processing algorithms can be applied such as automatic notch filters, adaptive channel equalization, noise reduction, noise blanking, and feedforward automatic gain control. Correcting bugs, improving performance or adding new features is as simple as downloading new software.

Following an overview of SDR systems, the details of the various blocks used in such systems, including analog-digital conversion,

are then explored. The chapter concludes with a discussion of the basic theory of discretetime and digital signals, with emphasis on topics relevant to radio communications.

# 8.2.1 SDR Architecture Options

The transition between analog and digital signals can occur at any of several places in the signal chain between the antenna and the user interface. This choice is an important factor in determining the overall architecture of the SDR. This section presents several block-diagram-level concepts for software-defined radio and compares architecture options.

#### **DSP AT AUDIO FREQUENCIES**

The initial use of DSP by amateur radio operators was to implement audio-frequency filtering. By the early 1990s, converter costs were reasonable and the processing power required was available in relatively inexpensive microprocessors with enhanced math function capability. The flexibility of digital filters (see the **Analog and Digital Filtering** chapter) and the ability to alter bandwidth and perform noise reduction resulted in quick adoption of DSP techniques in amateur equipment.

In 1992, Dave Hershberger, W9GR, designed an audio-frequency DSP filter based on the TMS320C10, one of the earliest practical DSP chips available. This filter was an external standalone unit that plugged into the headphone jack of a receiver and included filters with various bandwidths, an automatic multi-frequency notch filter, and an adaptive noise filter.

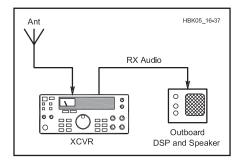

The advantage of DSP at audio frequencies is that it can be easily added to an unmodified analog radio as in **Figure 8.2**. Many amateurs use a similar approach to implement digital modulation modes, using a PC and software as the outboard DSP processor. The software produces the required transmission wave-

Figure 8.2 — An outboard DSP audio processor.

forms (and demodulates the received signal), using the PC's audio input and output connected to the audio input and output of a conventional SSB transceiver.

### **DOWNCONVERSION TO ANALOG BASEBAND**

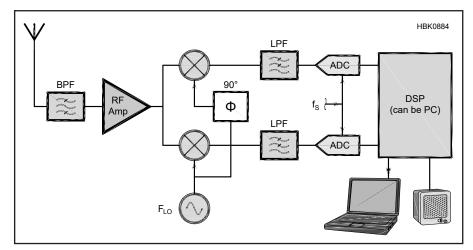

A related technique is to downconvert a slice of the radio spectrum to baseband audio using a technique similar to the directconversion receivers popular with simple lowpower CW transceivers. (See the Receiving chapter.) This idea was pioneered by Gerald Youngblood, AC5OG (now K5SDR), with the SDR-1000 transceiver, which he described in a series of QEX articles in 2002 and 2003.<sup>3</sup> The receiver block diagram is shown in **Fig**ure 8.3. It uses a unique I/Q demodulator designed by Dan Tayloe, N7VE, to convert the RF frequency directly to baseband I ("Inphase") and Q ("Quadrature") signals.4 (I/Q modulation and quadrature signals are discussed in the Modulation chapter.)

The baseband signals are fed to the stereo input of a PC's sound card, represented by the low-pass filters and analog-to-digital converters (A/D, or ADC) in the figure. Software in the PC does all the signal processing and demodulation, ultimately producing audio for the operator to hear or a display of decoded bits in the form of text on the screen. The transmitter is the same block diagram in reverse, with an I/Q modulator converting the I/Q signal from the sound card up to the RF frequency where it is filtered and amplified to the final power level.

The sound card method manages to achieve reasonable performance with simple, inexpensive hardware and resources already available in the PC. Once the A/D converters in the sound card have digitized the signal, the DSP capability of the PC can do amazing things with it. In addition to implementing conventional transceiver functions such as

several types of detector, variable-bandwidth filters, software AGC, an S-meter and speech compression, the software can include some extra features such as an automatic notch filter, noise reduction, panadapter and waterfall spectrum displays and decoding of signals such as RTTY, PSK, and WSJT modes.

The simple hardware of the SDR-1000 does impose some performance limitations. Because of imperfections in the analog downconverter, unwanted-sideband rejection is not perfect. This is called "image rejection" in the SDR-1000 literature. On the panadapter display, strong signals show up weakly on the opposite side of the display, equallyspaced from the center. DC offset in the analog circuitry causes a spurious signal to appear at the center of the bandwidth. To prevent an unwanted tone from appearing in the audio output, the software demodulator is tuned slightly off frequency, but that means interference at the image frequency can cause problems because of the imperfect image rejection.

The dynamic range depends on the sound card performance as well as the RF hardware. Some newer SDRs include an integrated audio codec or other type of A/D and D/A converters optimized for the application so that the PC's sound card is not needed.

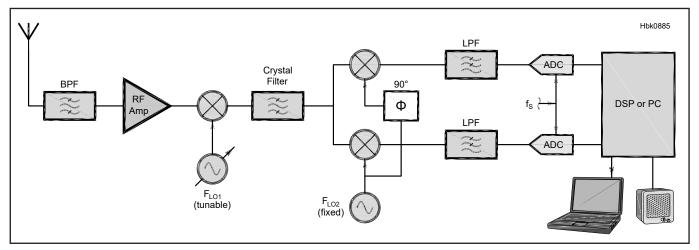

#### **DIGITIZING AT IF**

Another option for implementing softwaredefined radios involves performing the analog-digital conversion at an intermediate frequency. Figure 8.4 shows such a design. In the receiver, placing the A/D converter after a crystal IF filter improves the blocking dynamic range (BDR) for interfering signals that fall outside the crystal filter bandwidth. BDR is the ratio, expressed in dB, between the noise level (normally assuming a 500 Hz bandwidth) and an interfering signal strong enough to cause 1 dB gain reduction of the desired signal. (See the **Receiving** chapter.) As shown, the downconversion to I/Q format still uses lower-speed A/D converters, but

Figure 8.3 — Direct-to-baseband SDR receiver architecture.

Figure 8.4 — Hybrid superhet/DSP SDR receiver architecture.

often the signal is actually at a low IF, say, 15 kHz or so. This allows an SSB-bandwidth signal to be contained within the 20 kHz bandwidth of a typical audio codec and avoids errors due to dc offsets in the signal path. With careful design, a receiver with such an architecture can achieve 140 dB or more of BDR (if there are no other limiting factors such as LO phase noise). The third-order dynamic range is similar to that achieved with a conventional analog architecture since the circuitry up to the crystal filter, including amplifiers and mixer(s) is the same. The Elecraft K3 and Icom IC-7851 transceivers used this architecture and achieved very high receiver performance.

An advantage of the IF-based approach compared to directly sampling the RF frequency is that the ADC does not have to run at such a high sample rate. In fact, because the crystal filter acts as a high-performance, narrow-bandwidth anti-aliasing filter, *undersampling* is possible if the A/D converter has sufficient sampling bandwidth (ADCs intended for audio applications generally do not). With bandwidths of a few kHz or less, sample rates in the tens of kHz can be used even though the center frequency of the IF signal is much higher, so long as the ADC's sample-and-hold circuit has sufficient bandwidth.

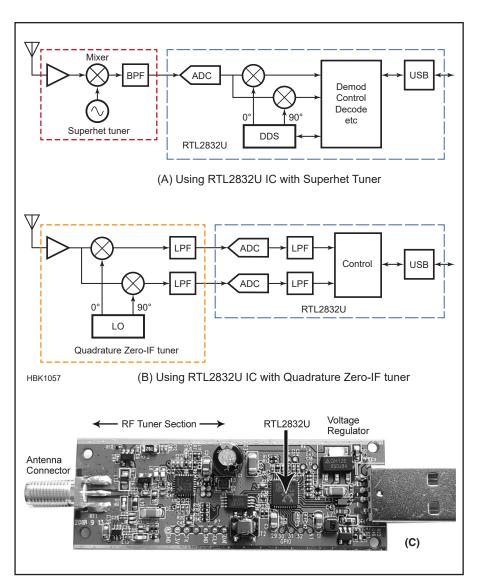

Another example of an IF-sampling SDR is the family of "SDR dongles" based on chips designed for satellite TV applications such as the RTL2832U manufactured by Realtek. Several different manufacturers produce such devices. The RTL2832U IC includes a pair of 8-bit A/D converters operating at a 28.8 Msps sample rate and a programmable DSP system including digital low-pass filters, demodulation, decoding, and other functions. The outputs of the A/D converters and the outputs of the digital processor are accessible via the chip's integrated USB port. The RTL2832U device is usually preceded by a either a superheterodyne (superhet) or quadrature zero-IF tuner. With a superhet receiver, only one of the on-chip ADCs is used, and the RTL2832U does the quadrature downconversion digitally. Bandwidth-limited IFs up to 30+ MHz can be undersampled. With a quadrature zero-IF downconverting tuner, both ADCs are used. You can find a more detailed description of implementation options using this IC at www.pa3fwm.nl/ technotes/tn20.html. A typical design (of many available), developed by RTL-SDR. com is shown in Figure 8.5C.

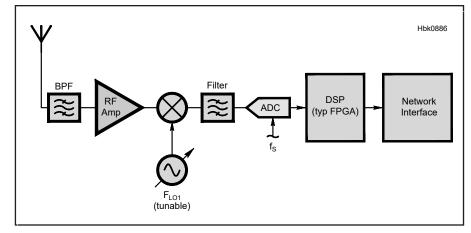

Some systems, especially in VHF/UHF/microwave applications such as cellular base stations which deal with signals that are tens of MHz wide and in the GHz frequency range, often use the approach shown in **Figure 8.6**. Here, a high-speed, high-bandwidth ADC digitizes an IF typically in the hundreds of

Figure 8.5 — Low cost SDR receiver using RTL2832U IC with a superhet tuner (A) and quadrature zero-IF tuner (B). An RTL-SDR dongle (C) plugs into a PC USB port. (photo courtesy of RTL-SDR.com)

Figure 8.6 — High-IF sampling SDR receiver architecture.

MHz. The output data rate of such a converter is too high to be handled by a PC or even a low-cost programmable DSP microprocessor. The conversion from the original signal to baseband I/Q components, and then the demodulation to data streams for the network is done in dedicated digital hardware blocks.

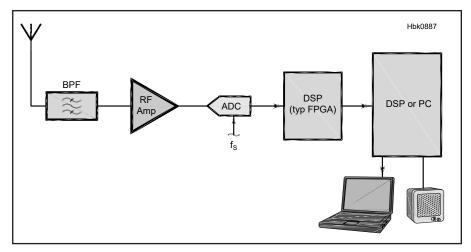

### **DIRECT RF DIGITIZING**

The ultimate SDR architecture is to convert between the analog and digital domains right at the frequency to be transmitted or received or convert a wide range of frequencies and do all filtering in the digital domain. The receive path of such a design is shown in Figure 8.7. In this receiver, the only remaining analog components in the signal chain are a wideband anti-aliasing filter similar to a preselector and an amplifier to improve the noise figure of the ADC if necessary. The FlexRadio Flex-6700, Elecraft K4, and Icom IC-7610 are examples of transceivers that use this basic architecture. The local oscillator, mixer, IF filters, AGC, demodulators and other circuitry are all replaced by digital hardware and software. The digital/software implementations of these functions are perfectly stable with time and temperature, and need no adjustments. The K4 DSP FPGA actually delivers three outputs: a wideband path for the panadapter display, and two 48-kHz IF outputs (for "dual-watch" capability) where the final high-performance filtering and demodulation occur.

### **HYBRID SDR/ANALOG RECEIVERS**

It has only been recently that low-cost highspeed ADCs have become available with specifications good enough to allow reasonable performance in an RF-sampling communications receiver. Today it is possible to achieve blocking dynamic range (BDR) of 130 dB. Hybrid SDR/analog receivers can provide even higher performance.

The highest performance receivers currently available for HF applications use both analog and DSP processing, with some amplification and filtering and analog downconversion to an intermediate frequency (and sometimes two downconversions) so that additional selectivity can be applied before the signal reaches the ADC. This approach is used in the Elecraft K3 and Icom IC-7851 transceivers.

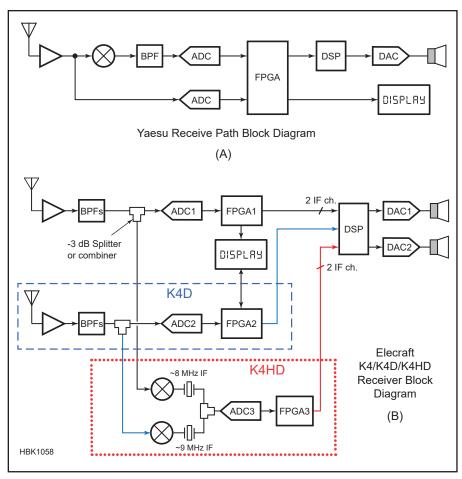

Figure 8.8 shows two examples of hybrid receiver chains. The Yaesu FTDX101 series transceivers use two receive signal chains. One is a direct RF sampler which is used only to provide a fast-responding digital band scope display. The other path which ultimately delivers audio to the user is a hybrid design, with a 9 MHz IF and optional narrow crystal filters, offering very high receiver performance.

Figure 8.7 — Direct RF-sampling DSP SDR receiver architecture.

Figure 8.8 — Receiver architectures of current high-performance transceivers — the Yaesu FTDX101 series (A) and Elecraft K4 (B). K4D and K4HD refer to model numbers, see text. (Figure 8.8B courtesy of Elecraft)

The Elecraft K4 platform has three versions. The K4D adds a second direct-sampling receiver to the basic K4 to provide diversity or dual-receive capability. The K4HD, intended for use in the most demanding environments, adds a two-channel hybrid signal chain to the K4D. Each channel includes an analog downconversion, one channel to an 8 MHz IF and one to a 9 MHz IF. These two analog IF signals are filtered by a bank of narrowband crystal filters, then combined and digitized by one A/D converter. The FPGA following this ADC delivers two 48 kHz digital IF signals to the DSP, which does the final filtering and demodulation as in the base model.

It is worth noting here that while huge BDR numbers can be measured in the laboratory, the performance achieved in a real-world environment with a receiver connected to an antenna is quite different. Often local noise sources raise the noise floor such that the receiver's full BDR cannot actually be utilized and other specifications become more important. In the real world, RF-sampling SDRs can often provide performance indistinguishable to conventional all-analog and hybrid receivers.

Third-order dynamic range (3IMD\_DR or IP<sub>3</sub>) is not a meaningful specification for this type of radio because it is based on the behavior of analog circuits which degrade gradually as the signal level increases. Calculation of 3IMD DR assumes that distortion products increase 3 dB for each 1 dB increase in signal level, which is not always true for an ADC. The level of the distortion products in an ADC tends to be more-or-less independent of signal level until the signal peak exceeds the ADC's full-scale input, at which point the distortion increases dramatically. It is important to read the data sheet carefully and note the test conditions for the distortion measurements.

There are definite advantages to sampling at RF. For one thing, it saves a lot of analog circuitry. Even though a high-speed ADC is more expensive than an audio converter, the radio may be end up being cheaper to build because of the reduced component count and fewer adjustments. Performance is improved in some areas. For example, image rejection is no longer a worry, as long as the anti-aliasing filter is doing its job. (See the **Receiving** chapter.) The dynamic range of an SDR theoretically does not depend on signal spacing — close-in dynamic range is often better than with a conventional architecture that uses a wide IF filter. With no crystal filters in the

signal chain, the entire system has a completely linear phase response, which can improve the quality of both analog and digital signals after demodulation.

The biggest challenge with RF sampling is what to do with the torrent of high-speed data coming out of the receiver's ADC and how to generate transmit data fast enough to keep up with the DAC sample rate. To cover 0 to 54 MHz without aliasing requires a sample rate of at least 120 or 130 MHz, and commercial products typically operate the ADC at sample rates well over 200 MHz. That is much faster than a typical microprocessor or programmable DSP can handle. The local oscillator, mixer, and decimator or interpolator must be implemented in digital hardware so that the DSP can send and receive data at a morereasonable sample rate. Digital downconverters (DDC) perform those functions and output a lower-sample-rate digital I/Q signal to the DSP. Stand-alone DDC ICs were available in the past, but the function is now usually integrated with the A/D converter. It is also possible to implement a DDC in a *field-pro*grammable gate array or FPGA. (See the Transceiver Design Topics chapter.) Digital upconverters (DUC) do the same conversion in reverse for the transmitter and are available integrated with the D/A converter or can be implemented in an FPGA. Some commercial integrated DDC/DAC products even include the capability to encode several digital modulation formats such as GMSK, QPSK and  $\pi/4$  DQPSK. In an attempt to simplify the interface to the digital domain, many highspeed converters now use a standardized serial interface specification called JESD204B, capable of handling up to 12Gb/s. Code to implement this interface on the digital FPGA is readily available.

Some designers have been successful in repurposing a graphics processor (GPU) for this application, and some GPU manufacturers now offer FFT libraries to assist in the design process.

# 8.2.2 Advantages and Limitations of DSP and SDR

Digital signal processing has the reputation of being more complicated than the analog circuitry that it replaces. In reality, once the analog signal has been converted into the digital domain, complicated functions can be implemented in software much more simply than would be possible with analog components. For example, the traditional "phasing"

method of generating an SSB signal without an expensive crystal filter requires various mixers, oscillators, filters and a wide-band audio-frequency phase-shift network built with a network of high-precision resistors and capacitors. To implement the same function in a DSP system requires adding one additional subroutine to the software program — and no additional hardware.

Many features that are straightforward with DSP techniques are difficult or impractical to implement with analog circuitry. A few examples drawn just from the communications field are imageless mixing, noise reduction, OFDM (orthogonal frequency division multiplexing) modulation and adaptive channel equalization. Digital signals can have much more dynamic range than analog signals, limited only by the number of bits used to represent the signal. For example, it is easy to add an extra 20 or 30 dB of headroom to the intermediate signal processing stages to ensure that there is no measurable degradation of the signal in a filter, for example. It would be difficult or impossible to add that much dynamic range with analog circuitry. Replacing analog circuitry with software algorithms eliminates the problems of nonlinearity and drift of component values with time and temperature. The programmable nature of most DSP systems means you can make the equivalent of circuit modifications without having to unsolder any components.

Despite its many advantages, we don't mean to imply that DSP is best in all situations. High-power and very high-frequency signals are still the domain of analog circuitry. Where simplicity and low power consumption are primary goals, a DSP solution may not be the best choice. For example, a simple CW receiver that draws a few milliamps from the power supply can be built with two or three analog ICs and a handful of discrete components. We are still a long way from that kind of low power radio using SDR.

In many high-performance systems, the performance of the analog-to-digital converter and digital-to-analog converter are the limiting factors. That is why, even with the latest generation of affordable ADC technology, it is still possible to obtain better blocking dynamic range in an HF receiver using a hybrid analog-digital system rather than going all-digital by routing the RF input directly to an ADC. This may change as A/D converter technology continues to evolve and performance rises.

### 8.3 Analog-Digital Conversion

Analog-to-digital (and digital-to-analog) conversion consists of taking data in one form, such as digital binary data or an analog ac RF waveform, and creating an equivalent representation of it in the opposite domain. Converters that create a digital representation of analog voltages or currents are called analogto-digital converters (ADC), analog/digital converters, A/D converters or A-to-D converters. Similarly, converters that create analog voltages or currents from digital quantities are called digital-to-analog converters (DAC), digital/analog converters, D/A converters or D-to-A converters. The word "conversion" in this first section on the properties of converting information between the analog and digital domains will apply equally to analog-to-digital or digital-to-analog conversion.

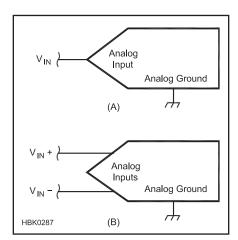

Converters are typically implemented as integrated circuits that include all of the necessary interfaces and sub-systems to perform the entire conversion process. In some cases, the converter may be integrated on the same chip as other analog functions (such as buffer amplifiers, reference voltages, etc.) or digital functions (such as digital filters). Schematic symbols for ADCs and DACs are shown in Figure 8.9.

This section defines the basic elements of analog-digital conversion along with an overview of different types of converters and their key specifications and behaviors. The following section discusses the use of converters for DSP and SDR functions which are the most demanding application in radio.

### 8.3.1 Basic Conversion **Metrics**

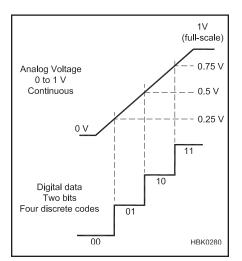

Figure 8.10 shows two different representations of the same physical phenomenon; an analog voltage changing from 0 to 1 V. In the analog world, the voltage is continuous and can be represented by any real number between 0 and 1. In the digital world, the number of possible values that can represent any phenomenon is limited by the number of bits contained in each value.

In Figure 8.10, there are only four two-bit digital values 00, 01, 10, and 11, each corresponding to the analog voltage being within a specific range of voltages. If the analog voltage is anywhere in the range 0 to 0.25 V. the digital value representing the analog voltage will be 00, no matter whether the voltage is 0.0001 or 0.24999 V. The range 0.25 to 0.5 V is represented by the digital value 01, and so forth.

The process of converting a continuous range of possible values to a limited number of discrete values is called digitization and

Figure 8.9 — Schematic symbols (A) for digital-to-analog converters (DAC) and analogto-digital converters (ADC). The general block diagram of a system (B) that digitizes an analog signal, operates on it as digital data, then converts it back to analog form.

Figure 8.10 — The analog voltage varies continuously between 0 and 1 V, but the two-bit digital system only has four values to represent the analog voltage, so representation of the analog voltage is coarse.

each discrete value is called a *code* or a *quan*tization code. If the code is a binary number, the number of possible codes that can represent an analog quantity is 2N, where N is the number of bits in the code. A two-bit number can have four codes as shown in Figure 8.10, a four-bit number can have sixteen codes, an eight-bit number 256 codes, and so forth. Assuming that the smallest change in code values is one bit, that value is called the *least* significant bit (LSB) regardless of its position in the format used to represent digital numbers.

Binary-coded-decimal (BCD) is a code in which groups of four bits represent individual decimal values of 0 - 9. In the hexadecimal code, groups of four bits represent decimal

values of 0 - 15 and are represented by the digits 0-9 followed by the letters A through F. Other types of codes that may be encountered include Gray code and octal.

### RESOLUTION AND RANGE

The resolution or step size of the conversion is the smallest change in the analog value that the conversion can represent. The range of the conversion is the total span of analog values that the conversion can process. The maximum value in the range is called the full-scale (F.S.) value. In Figure 8.10, the conversion range is 1 V. The resolution of the conversion is

$$resolution = \frac{range}{2^N}$$

In Figure 8.10, the conversion resolution is  $\frac{1}{4} \times 1 \text{ V} = 0.25 \text{ V}$  in the figure. If each code had four bits instead, it would have a resolution of  $\frac{1}{2}$  × 1 V = 0.0625 V. Conversion range does not necessarily have zero as one end point. For example, a conversion range of 5 V may span 0 to 5 V, -5 to 0 V, -2.5 to +2.5 V, and so on.

Analog-digital conversion can have a range that is *unipolar* or *bipolar*. Unipolar means a conversion range that is entirely positive (or negative), usually referring to voltage. Bipolar means the range can take on both positive and negative values.

Because each code represents a range of possible analog values, the limited number of available codes creates quantization error. This is the maximum variation in analog values that can be represented by the same code. In Figure 8.10, any value from 0.25 through 0.50 V could be represented by the same code: 01. The quantization error in this case is 0.25 V.

Resolution can also be defined by the number of bits in the conversion. The higher the number of bits, the smaller the resolution as demonstrated above. Since many converters have variable ranges set by external components or voltages, referring to percent resolution or as a number of bits is preferred. The conversions between percent resolution and number of bits are as follows:

% resolution =

$$\frac{1}{2^N} \times 100\%$$

and

$$N = \frac{\log\left(\frac{100\%}{\% resolution}\right)}{\log 2}$$

Quantization error can also be specified as a number of least significant bits (LSB) where each bit is equivalent to the conversion's resolution.

### **ACCURACY**

The number of bits of an A/D converter's resolution does not equate to the accuracy of the converter. A companion to resolution, accuracy refers to the ability of the converter to either assign the correct code to an analog value or create the true analog value from a specific code. As with resolution, it is most convenient to refer to accuracy as either a percentage of full scale or in bits. Full-scale error is the maximum deviation of the code's value or the analog quantity's value as a percentage of the full scale value. If a converter's accuracy is given as 0.02% F.S. and the conversion range is 5 V, the conversion can be in error by as much as  $0.02\% \times 5 \text{ V} = 1 \text{ mV}$  from the correct or expected value. Most A/D converters include provision for user adjustment to calibrate the converter's full-scale range. Some A/D converters include a reference voltage source internal to the device, while others require an external reference. External references can often provide higher accuracy and stability over temperature than internal references. Offset has the same meaning in conversion as it does in analog electronics — a consistent shift in the value of the conversion from the ideal value. It can also be adjusted if necessary by the user.

Linearity error represents the maximum deviation of the code transition points from the ideal code transition points after adjusting for the full scale and errors. This is also called integral nonlinearity (INL). In the converter of Figure 8.10, ideal step transitions occur at 0.25 V intervals. If the linearity error for the conversion was given as 0.05% F.S., any actual step size could be in error by as much as  $0.05\% \times 5 \text{ V} = 2.5 \text{ mV}$  due to the transition to the next step being at the wrong point. Differential nonlinearity is a measure of how much any two adjacent step sizes deviate from

the ideal step size. Errors can be represented as a number of bits, usually assumed to be least significant bits, or LSB, with one bit representing the same range as the conversion resolution. A typical A/D converter may specify its INL or DNL error as  $\pm$  0.5 LSB (least-significant bits).

### CONVERSION RATE AND BANDWIDTH

Another important parameter of the conversion is the *conversion rate* or its reciprocal, *conversion speed*. A digital code that represents an analog value at a specific time is called a *sample*, so conversion rate,  $f_S$ , is specified in *samples per second* (sps) and conversion speed as some period of time per sample, such as 1 msec. Because of the mechanics by which conversion is performed, conversion speed can also be specified as a number of cycles of clock signal used by the digital system performing the conversion. Conversion rate then depends on the frequency of the clock.

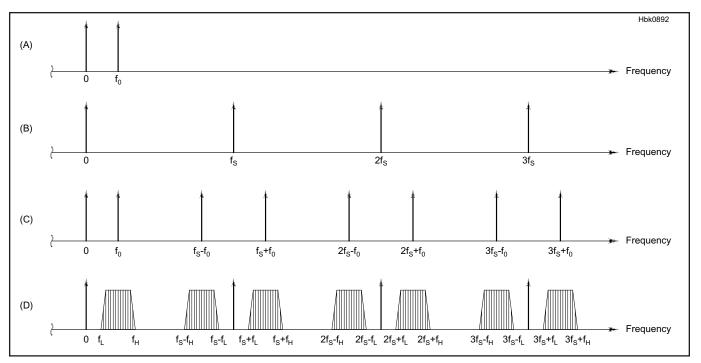

According to the *Nyquist Sampling Theorem*, in order to accurately represent the input signal, a conversion must occur at a rate at least twice the bandwidth of the analog signal. This minimum rate is the *Nyquist rate* and the maximum frequency allowed in the analog signal is the *Nyquist frequency*. In this way, the converter *bandwidth* is limited to one-half the conversion rate.

Referring to the process of converting analog signals to digital samples, if a lower rate is used, called *undersampling*, false signals called *aliases* will be created in the digital representation of the input signal at frequencies related to the difference between the Nyquist sampling rate and f<sub>S</sub>. This is called *aliasing*. Sampling faster than the Nyquist rate is called *oversampling* and can be used to advantage by following the converter with ah digital filter.

Because conversions occur at some maximum rate, there is always the possibility of signals greater than the Nyquist frequency being present in an analog signal undergoing conversion or that is being created from digital values. These signals would result in aliases and must be removed by *band-limiting filters* that remove them prior to conversion.

The mechanics of the sampling process are discussed later in this and following chapters as they apply to specific functions.

#### **DISTORTION AND NOISE**

Distortion and noise in a conversion are characterized by several parameters all related to linearity and accuracy. THD+N (Total Harmonic Distortion + Noise) is a measure of how much distortion and noise is introduced by the conversion. THD+N can be specified in percent or in dB. Smaller values are better. SINAD (Signal to Noise and Distortion Ratio) is related to THD+N, generally specified along with a desired signal level to show what signal level is required to achieve a certain level of SINAD or the highest signal level at which a certain level of SINAD can be maintained. (See the Analog Devices application note MT-003 by Kester in the Bibliography for further information about SINAD and other noise metrics.)

#### **ADC OVERLOAD**

When *overloaded*, A/D converters behave similarly to amplifiers driven into saturation or clipping. Consider the output of an ADC for various inputs as shown in **Table 8.1**. (This example assumes a 16-bit resolution and offset binary code). "–FS" and "+FS" are the negative and positive Full-Scale input voltage levels of the ADC.

This table shows the ADC cannot distinguish between an input signal exactly at the top (or bottom) of its range and a signal that exceeds the input range. In fact, the ADC cannot tell if the input range has been slightly exceeded or grossly exceeded. This is an example of *hard clipping*.

Fortunately, most ADCs have an output signal to indicate the input range has been exceeded and the converter is in *overload* or *overflow/underflow* mode. This allows the system designer to take appropriate action — usually reducing the gain of an amplifier or increasing the attenuation of any stages ahead of the ADC.

In designing an SDR system, careful attention must be given to the peak signal reaching the A/D converter. Long periods of overload can create artifacts in the DSP after the converter. RF signal levels are usually expressed

Table 8.1

Output of an ADC for Various Inputs

| Input voltage                                                                          | Output code (binary)                      | Output code (decimal)             |

|----------------------------------------------------------------------------------------|-------------------------------------------|-----------------------------------|

| At or below -FS<br>Just above -FS<br>Middle of range<br>Just below +FS<br>At +FS-1 LSB | 0000 0000 0000 0000<br>0000 0000 0000 000 | 0<br>1<br>32768<br>65534<br>65535 |

| At or above +FS                                                                        | 1111 1111 1111 1111                       | 65535                             |

in terms of power, rather than voltage, and often a signal is assumed to be a single sine wave. In a wideband receiver, the input signal is really the sum of many uncorrelated signals in the passband of the system, most of which are not even close to sinusoids.

In the **Radio Fundamentals** chapter, it is explained that ac waveforms are best characterized by their RMS (root-mean-square) values, and that a sine wave has an RMS value of 0.707 times the peak value. That means the peak value of the ac signal is 1.414 times the RMS value. This ratio is the *crest factor*. In terms of voltage, the 1.414 ratio is equal to 20 log (1.414), which is 3.01 dB. In terms of power, the 1.414 voltage ratio is a power ratio of (1.414)<sup>2</sup>, which is 10 log (2), which is also 3.01 dB.

Other waveforms have different crest factors. A triangle wave has a crest factor of 1.732, or 4.77 dB. Signals that include multiple individual signals within the passband of the A/D converter tend to look almost like noise, which has a high crest factor (true Gaussian noise has an infinite crest factor!). In addition, some environments have locallygenerated noise from sources such as powerline leakage or arcing, electric fences, or nearby switch-mode power supplies, not to mention atmospheric noise. Any of these can cause an A/D converter to overload.

Typical high-speed A/D converters are high-input-impedance devices and require a dc bias or offset on the input waveform when operated from a single-polarity power source. The input signal from preceding stages is usually transformer-coupled to the A/D converter input, biased from a signal generated by the A/D converter. Converter manufacturers usually give excellent guidance on how to couple the signal into the converter for optimal performance. Most ADCs utilize an input voltage range on the order of 2 V<sub>P-P</sub>. It is good practice to plan for several dB of overhead in the signal level reaching the A/D converter. Allowing for 10 dB of headroom means that the expected signal levels should only use about 1/3 of the A/D converter's input voltage range.

# 8.3.2 Analog-to-Digital Converters

There are a number of methods by which the conversion from an analog quantity to a set of digital samples can be performed. Each method or *architecture* has its strong points — simplicity, speed, resolution, accuracy — all affect the decision of which method to use for a particular application. In order to pick the right type of ADC, it is important to decide which of these criteria most strongly affect the performance of your application.

The following sections present ADC architectures used in amateur radio from the fastest to progressively slower conversion. For a

more complete review of ADC architectures, see Kester's article "Which ADC Architecture Is Right for Your Application?" listed in the Reference section.

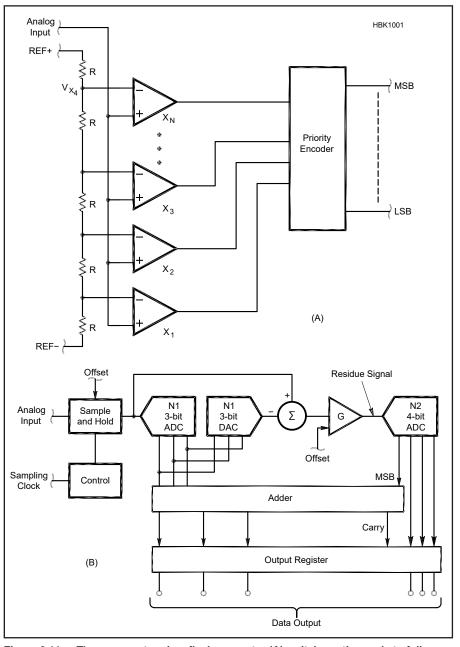

#### **FLASH CONVERTER**

The simplest type of ADC is the *flash converter*, shown in **Figure 8.11**. It continually generates a digital representation of the analog signal at its input. The flash converter uses an array of comparators that compare the amplitude of the input signal to a set of reference voltages. There is one reference voltage for each step.

The outputs of the comparator array represent a digital value in which each bit indicates whether the input signal is greater (1) or less than (0) the reference voltage for that comparator. A digital logic *priority encoder* then converts the array of bits into a digital output code. Each successive conversion is available as quickly as the comparators can respond and the priority encoder can create the output code. Flash converters are generally used for applications in which high speed is more important than bits of resolution.

Flash converters are the fastest of all ADCs (conversion speeds can be in the nanosecond

Figure 8.11 — The comparators in a flash converter (A) switch continuously to follow the input signal. The encoder converts the array of comparator outputs to a single digital word. Flash converters (N1 and N2) form the basis of the pipelined converter (B) that is used at the very high sample rates needed for SDR applications.

range, equivalent to sampling rates in the gigasamples/second) but do not have high resolution because of the number of comparators and reference voltages required. For example, an 8-bit flash converter requires 255 comparators, while a 12-bit version would require 4095 comparators.

One specialized variant of the flash converter is the *bar-graph display driver*. Such devices accept an analog input and deliver output signals capable of directly driving an LED display rather than a binary digital output word. These devices are commonly used to replace meters as front panel displays for signals that represent relatively slow-varying parameters such as transmitter output power. The LM3914 from Texas Instruments is one such device.

#### **PIPELINED CONVERTER**

A pipelined converter uses two or more stages of flash converters as shown in Figure 8.11B. The output of the first stage flash converter (N1) is changed back to an analog signal by a DAC and the difference between the DAC output and input signal is called the residue signal. The residue signal is amplified then digitized by a second flash converter (N2). The digital outputs of the two flash converters are combined by an adder and a register to create the overall converter output word. The digital outputs of multiple stages can be combined to yield more bits than a single-stage flash converter would produce. Pipelined converters are discussed in additional detail in the section Data Converters for SDR and DSP later in this chapter.

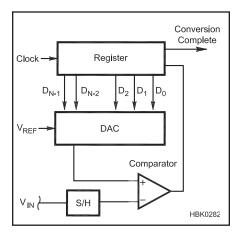

### SUCCESSIVE-APPROXIMATION CONVERTER

The *successive-approximation* A/D converter is one of the most widely-used types of converters. As shown in **Figure 8.12**, it uses a single comparator and DAC (digital-to-analog converter) to arrive at the value of the input voltage by comparing it to successive analog values generated by the DAC. This type of converter offers a good compromise of conversion speed and resolution.

The control logic begins a conversion by setting the output of the DAC to ½ of the conversion range. If the DAC output is greater than the analog input value, the output of the comparator is 0 and the most significant bit of the digital value is set to 0. If the DAC output is less than the analog input, the bit is set to 1. The DAC output then either increases or decreases by 1/4 of the range, depending on whether the value of the first comparison was 1 or 0. At this point the input voltage is being compared to either 1/4 of the scale or 3/4 of the range. One test is made for each bit in digital output code and the result accumulated in a storage register, called the Successive-Approximation Register, which is why such

Figure 8.12 — The successive-approximation converter creates a digital word as it varies the DAC signal in order to keep the comparator's noninverting terminal close to the input voltage. A sample-and-hold circuit (S/H) holds the input signal steady while the measurement is being made.

converters are often called "SAR" converters. The process is then repeated, forming a series of approximations, until a test has been made for all bits in the code.

While the digital circuitry to implement the SAR converter is more complex, it is less expensive to build and calibrate than the array of comparators and precision resistors of the flash converter, especially for higher resolutions. Each conversion also takes a known and fixed number of clock cycles. SAR A/D converters are used for speeds up to a few Msps. They are often used with an analog multiplexer in front so that multiple signals in a system can be measured relatively quickly, rather than using a separate converter for every signal.

### DUAL-SLOPE INTEGRATING CONVERTERS

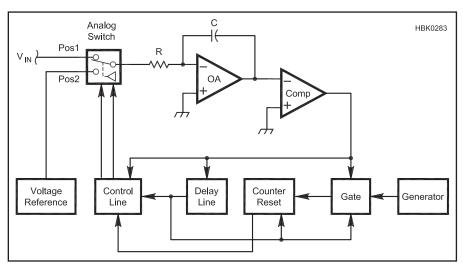

The *dual-slope integrating ADC* is shown in **Figure 8.13**. It makes a conversion by integrating the input signal by charging a capac-

Figure 8.13 — Dual-slope integrating converter. By using a constant-current source to continually charge a capacitor to a known reference voltage then discharge it, the resulting frequency is directly proportional to the resistor value.

Figure 8.14 — Delta-encoded converter. The 1-bit DAC is operated in such a way that the bit stream out of the comparator represents the value of the input voltage.

itor for a fixed period of time then measuring the time it takes for the capacitor to discharge back to its starting value. The integration period is often set to reject an interfering signal by integrating it over an exact number of cycles. For example, setting the integration period to 100 milliseconds results in 6 full cycles of a 60 Hz sinusoidal interferer and 5 full cycles of a 50 Hz interferer.

Dual-slope ADCs are low-cost and relatively immune to temperature variations. Due to the slow speed of the conversion these converters are generally only used in test instruments such as multimeters or for measurement of slowly-varying dc signals.

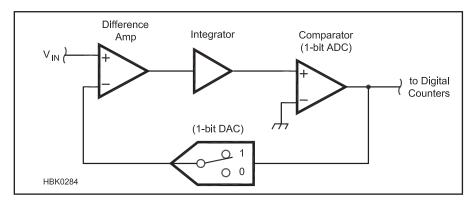

#### **DELTA-ENCODED CONVERTERS**

Instead of charging and discharging a capacitor from 0 V to the level of the input signal, and then back to 0 V, the delta-encoded ADC in Figure 8.14 continually compares the output of a DAC to the input signal using a comparator. Whenever the signal changes, the DAC is adjusted until its output is equal to the input signal. Digital counter circuits keep track of the DAC value and generate the digital output code.

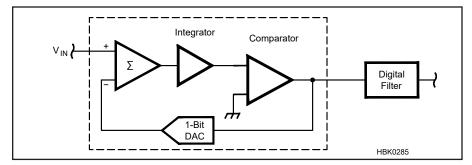

#### **SIGMA-DELTA CONVERTERS**

The sigma-delta converter also uses a DAC and a comparator in a feedback loop to generate a digital signal as shown in Figure 8.15. An integrator stores the sum of the input signal and the DAC output. (This is "sigma" or sum in the converter's name.) The comparator output indicates whether the integrator output is above or below the reference voltage and that signal is used to adjust the DAC's output so that the integrator output stays close to the reference voltage. (This is the "delta" in the name.) The stream of 0s and 1s from the comparator forms a high-speed digital bit stream that is digitally-filtered to form the output code. Sigma-delta converters are used where high resolution (16 to 24 bits) is required at sampling rates in the ksps range, including very slowly-varying signals and even audio signals.

### 8.3.3 Analog-to-Digital **Converter Subsystems**

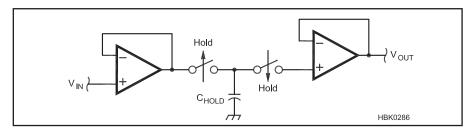

### SAMPLE-AND-HOLD

ADCs that use a sequence of operations to create the digital output code must have a means of holding the input signal steady while the measurements are being made. This function is performed by the circuit of **Figure 8.16**. A high input-impedance buffer drives the external storage capacitor, C<sub>HOLD</sub>, so that its voltage is the same as the input signal. Another high input-impedance buffer is used to provide a replica of the voltage on C<sub>HOLD</sub> to the conversion circuitry.

Figure 8.15 — Sigma-delta converter. Similar to the delta-encoded converter (Figure 8.14), the converter runs much faster than the output samples and uses a digital filter to derive the actual output value.

Figure 8.16 — Sample-and-hold (S/H). An input buffer isolates the sampled voltage from the input signal by charging the capacitor C<sub>HOLD</sub> to that voltage with the input switch closed and the output switch open. When a measurement is being taken, the input switch is open to prevent the input signal from changing the capacitor voltage, and the output switch is closed so that the output buffer can generate a steady voltage at its output.

Figure 8.17 — Single-ended ADC inputs have a single active line and a ground or return line (A). Single-ended ADC input are often susceptible to noise and common mode signals or any kind of disturbance on their ground rails. In (B), the differential inputs used help the circuit "ignore" offsets and shifts in the input signal.

When a conversion is started, a digital control signal opens the input switch, closes the output switch, and the capacitor's voltage is measured by the converter. It is important that the capacitor used for CHOLD have low leakage so that while the measurement is being made, the voltage stays constant for the length of time required to complete the conversion process. This is of particular important in high-precision conversion.

### SINGLE-ENDED AND **DIFFERENTIAL INPUTS**

The input of most ADCs is *single-ended*, in which the input signal is measured between the input pin and a common ground. Shown in Figure 8.17A, this is acceptable for most applications, but if the voltage to be measured is small or is the difference between two nonzero voltages, an ADC with differential inputs should be used as in Figure 8.17B. Differential inputs are also useful when measuring current as the voltage across a small resistor in series with the current. In that case, neither side of the resistor is likely to be at ground, so a differential input is very useful. Differential inputs also help avoid the issue of noise contamination as discussed below.

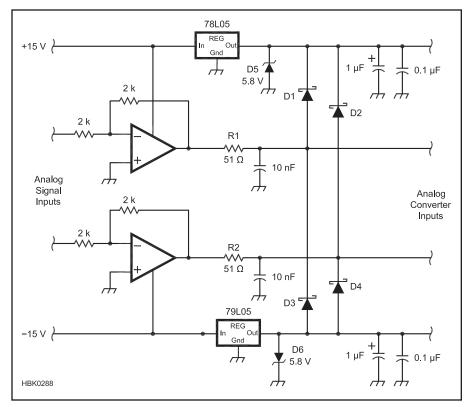

### INPUT BUFFERING AND FILTERING

The input impedance of most ADCs is high enough that the source of the input signal is unaffected. However, to protect the ADC input and reduce loading on the input source, an external buffer stage can be used. Figure 8.18 shows a typical buffer arrangement with clamping diodes to protect against electrostatic discharge (ESD) and an RC-filter to

Figure 8.18 — Typical ADC input buffer-filter circuit. Unity-gain voltage followers help isolate the ADC from the input source. RC filters following the buffers act as band-limiting filters to prevent aliasing. Zener diodes are used to clamp the transient voltage and route the energy of transient into the power supply system.

Figure 8.19 — Summing DAC. The output voltage is the inverted, weighted sum of the inputs to each summing resistor at the input. Digital data at the input controls the current into the summing resistors and thus, the output voltage.

prevent RF signals or noise from affecting the input signal. In addition, to attenuate higher-frequency signals that might cause aliases, the input filters can also act as band-limiting filters.

### **ANALOG AND DIGITAL "GROUND"**

By definition, ADCs straddle the analog and digital domain. In principle, the signals remain separate and isolated from each other. In practice, however, voltages and currents from the analog and digital circuitry can be mixed together. This can result in the contamination of an analog signal with components of digital signals, and rarely, vice versa. Mostly, this is a problem when trying to measure small voltages in the presence of large power or RF signals.

The usual problem is that currents from high-speed digital circuitry find their way into analog signal paths and create transients and other artifacts that affect the measurement of the analog signal. Thus, it is important to have separate current paths for the two types of

signals. The manufacturer of the converter will provide guidance for the proper use of the converter either in the device's data sheet or as application notes. Look for separate pins on the converter, such as "AGND" (Analog Ground) or "DGND" (Digital Ground) that indicate how the two types of signal return paths should be connected.

# 8.3.4 Digital-to-Analog Converters (DAC)

Converting a digital value to an analog quantity is considerably simpler than the reverse, but there are several issues primarily associated with DACs that affect the selection of a particular converter.

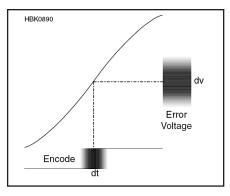

As each new digital value is converted to analog, the output of the DAC makes an abrupt step change. Even if very small, the response of the DAC output does not respond perfectly or instantaneously. Settling time is the amount of time required for the DAC's output to stabilize within a certain amount of the final value. It is specified by the manufacturer and can be degraded if the load connected to the DAC is too heavy or if it is highly reactive. Settling time is critical in control applications and also sets the limit on update sampling rate.

Monotonicity is another aspect of characterizing the DAC's accuracy. A DAC is monotonic if increasing the digital input value causes the output of the DAC to increase with every step. Because of errors in the internal conversion circuitry, it is possible for there to be some steps that are too small or too large, leading to output values that seem "out of order." These are usually quite small, but if used in a precision control application where the DAC is part of a feedback loop, monotonicity is important because the control system can go unstable.

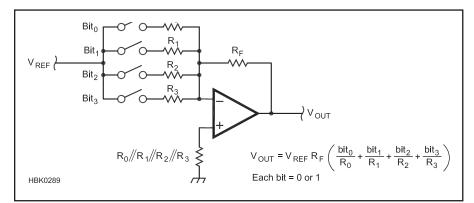

#### **SUMMING DAC**

A summing DAC, shown in **Figure 8.19**, is a summing amplifier with all of the inputs connected to a single reference voltage through switches. The digital value to be converted controls which switches are closed. The larger the digital value, the more switches are closed. Higher current causes the summing amplifier's output voltage to be higher, as well.

The input resistors are binary-weighted so that the summing network resistors representing the more significant bit values inject more current into the op amp's summing junction. Each resistor differs from its neighboring resistors in the amount of current it injects into the summing node by a factor of two, recreating the effect of each digital bit in the output voltage. At high resolutions, this becomes a problem because of the wide spread in resistor values — a 12-bit DAC

would require a spread of 2048 between the largest and smallest resistor values. Summing DACs are generally only available with low resolution for that reason.

The current output DAC functions identically to the summing DAC, but does not have an op amp to convert current in the digitallycontrolled resistor network to voltage. It consists only of the resistor network, so an external current-to-voltage circuit (discussed in the previous section on op amps) is required to change the current to a voltage. In some applications, the conversion to voltage is not required or it is already provided by some other circuit.

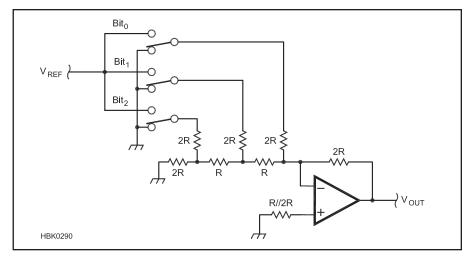

#### R-2R LADDER DAC

The summing and current output DACs both used binary weighted resistors to convert the binary digital value into the analog output. The practical limitation of this design is the large difference in value between the smallest and largest resistor. For example, in a 12-bit DAC, the smallest and largest resistors differ by a factor of 2048 (which is  $2^{12-1}$ ). This can be difficult to fabricate in an IC since it is difficult to match a wide range of resistors values closely enough to maintain the desired binary-weighted relationship with sufficient accuracy. For DACs with resolutions of 8 bits or more, the R-2R ladder DAC of Figure 8.20 is a better design. R-2R DACs can operate in either voltage mode or current mode.

The problems of manufacturing are greatly reduced when resistances are fairly close in value. By using the R-2R ladder shown in the figure, the same method of varying current injected into an op amp circuit's summing junction can be accomplished with resistors of only two values, R and 2R. In fact, since the op amp feedback resistor is also one of the IC resistors, the absolute value of the resistance R is unimportant, as long as the ratio of R:2R is maintained. This simplifies manufacturing greatly and is an example of IC design being based on ratios instead of absolute values. For this reason, most DACs use the R-2R ladder design and the performance differences lie mostly in their speed and accuracy.

Similar ladder networks can be constructed using capacitors. Such networks are used on many SAR-type A/D converters because in

Figure 8.20 — R-2R Ladder DAC. This is the most common form of DAC because all of the resistor values are similar, making it easier to manufacture. The similarity in resistor values also means that there will be less variation of the comparator with temperature and other effects that affect all resistors similarly.

some fabrication processes, capacitors are easier to make than resistors.

#### **DIGITAL POTENTIOMETERS**

Since D/A converters are commonly used to provide digitally-controlled adjustments, a special class of D/A converters has evolved, specifically intended for use as calibration/ adjustment devices. These are known as "digital potentiometers." They differ from traditional D/A converters in that they appear as three-terminal variable resistors of known value, and often include non-volatile control registers. They are specified in terms of resistance value, number of steps, and number of devices per package.

### 8.3.5 Choosing a Converter

From the point of view of performance, choosing a converter, either an ADC or a DAC, comes down to resolution, accuracy and speed. Begin by determining the percent resolution or the dynamic range of the converter. Use the equations in the preceding section to determine the number of bits the converter must have. Select from converters with the next highest number of bits. For example, if you determine that you need 7 bits of resolution, use an 8-bit converter.

Next, consider accuracy. If the converter is

needed for test instrumentation, you'll need to perform an error budget on the instrument's conversion processes, include errors in the analog circuitry. Once you have calculated percent errors, you can determine the requirements for FS error, offset error, and nonlinearities. If an ADC is going to be used for receiving applications, the spurious-free dynamic range may be more important than high DC precision.

The remaining performance criterion is the speed and rate at which the converter can operate. Conversions should be able to be made at a minimum of twice the bandwidth of the signal you wish to reproduce. If the converter will be running near its maximum rate, be sure that the associated digital interface, supporting circuitry, and software can support the required data rates, too!

Having established the conversion performance requirements, the next step is to consider cost, amount of associated circuitry, power requirements, and so forth. For example, a self-contained ADC is easier to use and takes up less PC board space, but may not be as accurate as one that allows the designer to use an external voltage reference to set the conversion range. Other considerations, such as the nature of the required digital interface, as discussed in the next section, can also affect the selection of the converter.

### 8.4 Data Converters for SDR and DSP

In this section we will focus more closely on converters for use with DSP and SDR. The first requirement when selecting a DAC or ADC is that it be able to handle the required *sample rate*. For communications-quality voice (300 – 3000 Hz), a sample rate on the order of 8000 samples per second (8 ksps) is adequate and has been used in the public switched telephone network for decades. For CD-quality music (20 – 20,000 Hz), the standard sample rate is 44.1 ksps, while 48 ksps and even 96 or 192 ksps are used for newer audio formats and applications such as professional studio equipment.

In an SDR system intended to use microphone inputs and speaker or headphone outputs, there is a need to convert between analog and digital at audio rates. Fortunately, combination A/D and D/A chips and software packages called codecs (short for coderdecoder) are readily available to do this job. Both "audio codecs," with sample rates consistent with high-fidelity audio up to 20 kHz or so, and "voice codecs," intended for voicequality audio up to 4 or 8 kHz) are available. The switched telephone network originally used 8-bit logarithmic codecs to digitize and reconstruct voiceband audio signals. Logarithmic coding was used to compress the dynamic range of a voice signal to reduce the number of bits to be transported.

Today, linear-coded devices have become preferable since DSP algorithms work on linear-coded data and often perform more efficient compression algorithms to reduce the number of bits needed to transport digitized voice. Since audio codecs are used in PC and other consumer systems they are very low cost (or are free if the PC is part of the SDR system). They have more than adequate performance for SDR applications dealing with relatively narrowband signals, such as CW, SSB, AM, and digital signals such as RTTY, PACTOR, and WSJT modes that use bandwidths comparable to SSB.

Processing wideband RF signals requires data converters with sample rates in the megasamples per second (Msps) range. Fortunately, manufacturers of digital communications infrastructure equipment for the cellular industry have similar needs, and manufacturers of data converter ICs have developed products that are produced in reasonable volume (which lowers the cost) and can be repurposed for amateur SDRs.

The resolution of a data converter expressed as the number of bits in the data words gives an approximation of the converter's signal-to-noise ratio. For example, an 8-bit ADC can only represent the sampled analog signal as one of  $2^8 = 256$  possible numbers. The smallest signal that it can resolve is therefore 1/256

of full scale. In terms of signal-to-noise ratio, the rule of thumb is 6 dB per bit, so an ideal 8-bit converter should have a dynamic range of about 48 dB.

The actual formula is slightly different. In an ideal, error-free ADC, the *quantization error* is up to  $\pm 1/2$  of one least-significant bit (LSB) of the digital word, or  $\pm 1/512$  of full scale with 8-bit resolution. Similarly, a DAC can only generate the analog signal to within  $\pm 1/2$  LSB of the desired value. These unavoidable errors are indistinguishable from noise in a signal-processing system.

It can be shown mathematically that a series of uniformly-distributed random numbers between +0.5 LSB and -0.5 LSB has an RMS value of

$$\frac{LSB}{\sqrt{12}}$$

This represents the quantization noise of an A/D.

The **Radio Fundamentals** chapter shows that a sinusoidal signal of 2 V peak-to-peak (1 V peak) has an RMS voltage equal to 0.707 V, or  $\sqrt{2}$  / 2 V. In the case of a full-scale sinusoidal signal applied to an ADC of N bits (2<sup>N</sup> LSBs), the RMS signal voltage can be written as  $(2^{N-1}LSB)/\sqrt{2}$ .

Combining that information results in the following equation for the signal-to-noise ratio in decibels for an ideal data converter word of width N bits:

$$SNR = 20\log\left(\frac{\frac{2^{N-1}LSB}{\sqrt{2}}}{\frac{LSB}{\sqrt{12}}}\right)$$

### **Distortion and Noise**

Distortion and noise in a conversion are characterized by several parameters all related to linearity and accuracy. THD+N (Total Harmonic Distortion + Noise) is a measure of how much distortion and noise is introduced by the conversion. THD+N can be specified in percent or in dB. Smaller values are better. SINAD (Signal to Noise and Distortion Ratio) is related to THD+N, generally specified along with a desired signal level to show what signal level is required to achieve a certain level of SINAD or the highest signal level at which a certain level of SINAD can be maintained. (See the Analog Devices application note MT-003 by Kester in the Bibliography for further information about SINAD and other noise metrics.)

which simplifies to

SNR = (6.02N + 1.76) dB

The extra 1.76 dB arises from the fact that noise has a lower RMS value than a sine wave for the same peak-to-peak amplitude. Therefore, with an ideal 8-bit converter, SNR = 49.9 dB. A perfect 16-bit ADC would achieve a 98.1 dB signal-to-noise ratio. Of course, real-world devices are never perfect so actual performance is always somewhat less. Internally-generated noise degrades the SNR, and errors in the linearity of the converter's transfer function give rise to distortion in the form of spurious spectral components and harmonics. (See also "Clocking the RFADC: Should you worry about jitter or phase noise?" a Texas Instruments application note available for download at www.ti.com/lit/an/slyt705/ slyt705.pdf.)

## 8.4.1 Using Audio ADCs for SDR

A/D and D/A converters used in audio systems and PC "sound cards" are often repurposed for use in hybrid SDRs. While they may offer as many as 24 bits of resolution, in reality audio A/D converters only provide 110 to 120 dB of SNR and "dynamic range," and the best "24-bit" audio D/A converters deliver 128 dB. According to the formula above, a 24-bit converter should have  $1.76 + (6.02 \times 24)$ , or 146.2 dB. What happened to the remaining 20 to 40 dB?

Part of the reason that audio converters use 24-bit data words is that the recording and playback formats for many systems (such as Blu-Ray Disc and studio equipment) are designed to accommodate 24-bit data words, even if the lower-order bits are essentially meaningless. For reference, a least-significant bit for a typical 24-bit audio converter with a 5 V p-p signal range is about 100 nanovolts (0.1 microvolts) and it is difficult to keep noise that low in the real world.

Furthermore, the testing of A/D converters intended for use in audio systems is different from how we might specify them for radio applications. For example, the "dynamic range" specification in digital audio systems is tested by measuring the THD+N (Total Harmonic Distortion plus Noise) for a 1 kHz input signal at a level 60 dB below full-scale, converting the number to a positive value, then adding 60. For example, an audio D/A converter that delivers THD+N of -51 dB under this test condition can be specified as having a dynamic range of 111 dB. While this is not the same way that communications systems define dynamic range, the goal of both audio and radio systems is to evolve

towards higher dynamic range, so the performance generally heads in the right direction in both fields.

#### SIGMA-DELTA CONVERTERS

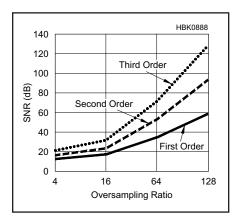

The noise spectrum of an A/D converter occupies the bandwidth from dc to one-half the sampling frequency, and is more-or-less uniformly spread out over that range. Thus, in any smaller slice of the output spectrum, the noise is much lower compared to the fullscale output of the converter. Thus, if we have an A/D converter sampling at a very high rate relative to the bandwidth of interest, and then add a digital filter after the A/D converter that eliminates the noise components outside the spectrum of interest, we can in principle increase the SNR in the desired bandwidth. An A/D conversion system that operates this way is said to be oversampling.

Oversampling by a factor of N improves the SNR in a given bandwidth by the square root of N since the number of samples of the desired signal is multiplied by N, and the noise, which is uncorrelated, increases as the square root of N. This can be simplified to 3 dB SNR improvement for every doubling of the sample rate. Thus, a 4× oversampling rate is equal to adding another bit of resolution to a converter.

Audio converters are an example of oversampled converters, and usually use a technique known as sigma-delta modulation. The sigma-delta converter introduced earlier uses a DAC and a comparator in a feedback loop to generate a digital signal. An integrator stores the sum of the input signal and the DAC output. This is "sigma" or sum in the converter's name. The comparator is in essence a one-bit A/D converter, and its output indicates whether the integrator output is above or below the reference voltage. That signal is used to adjust the DAC's output so that the integrator output stays close to the reference voltage. This is the "delta" in the name. The stream of 0s and 1s from the comparator forms

Figure 8.21 — The benefits of noise-shaping as the order of the sigma-delta converter feedback loop is increased.

a high-speed digital bit stream that is digitallyfiltered to form the output code, at a much lower output sample rate.

Most ADCs and DACs used in audio systems use an extreme form of oversampling, where the internal converter may oversample by a rate of 128 or 256 times the desired output rate. For example, the comparator of an audio A/D intended for a 48 ksps output rate may be clocked at  $256 \times 48$  ksps, or 12.288MHz. In addition, sigma-delta audio converters use a technique called noise shaping to push most of the quantization noise to frequencies above the audio band, thereby reducing it in the audio spectrum. Noise shaping is accomplished by adding more integrators in the feedback loop of the simple sigma-delta modulator to form a "higher-order loop" with a low-pass response for the signal, but a highpass response for the noise. The digital lowpass filter then removes the noise and produces output data words of higher width at the desired sample rate. The high input sampling rate of the converter also relaxes the requirements for external band-limiting (anti-aliasing) filters on the input signal. Figure 8.21 illustrates the relationship between loop order, sample rate, and improvements in signal-tonoise ratio.

Since audio A/D converters are the audio input device on many PC-based systems, they are quite inexpensive. The Left- and Rightchannel stereo inputs can be repurposed and renamed "I" and "Q" for use in SDR applications. Even if the converter specifications are not exactly ideal they provide adequate performance for a hybrid SDR.

### 8.4.2 High-Speed **ADCs for SDR**

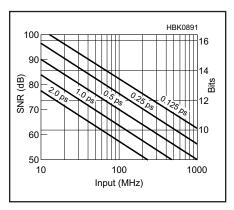

Commercial applications such as cellular base stations have driven the need for highspeed converters capable of sampling RF or high-IF signals directly. These have enabled the development of amateur radio HF transceivers using direct RF sampling. In addition to the usual specifications of linearity, etc., most manufacturers of high-speed data converters intended for use in wideband SDR systems now include a specification for spurious-free dynamic range (SFDR). This is the ratio, normally expressed in dB, between a (usually) full-scale sine wave and the worstcase spurious signal. It is a useful figure of merit for comparing such converters. (Highspeed SDR hardware from several manufacturers and vendors is addressed in the column "SDR: Simplified" by Ray Mack, W5IFS, in the January/February 2013 issue of QEX.)

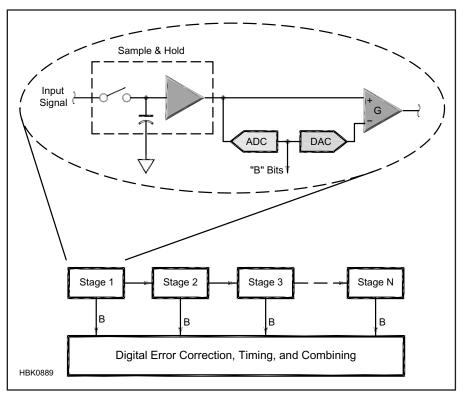

### PIPELINED ADC ARCHITECTURE

Most high-speed converters intended for SDR applications use a *pipelined* architecture. This type of A/D converter consists of multiple stages, each of which includes a sampleand-hold function, low-resolution A/D and D/A converter, and a gain stage. The first stage

Figure 8.22 — Block diagram of pipelined high-speed A/D converter.

Figure 8.23 — RMS jitter vs. RMS noise effect of sampling uncertainty on signal-to-noise. [from Figure 1 of Analog Devices Application Note AN-501, available at www.analog.com, used with permission]

performs a coarse quantization of the input signal, of say, "B" bits, where B is typically 1 to 4 in commercial products. The resultant data word is applied to a D/A converter, and the output analog voltage is subtracted from the original input signal, producing an error signal. That error signal is amplified and passed to another, usually identical, converter stage with enough overlap to compensate for any errors in the previous conversion. Many stages can be connected together, with the last stage only including an A/D converter. The digital outputs from each stage are combined and corrected, as well as time-aligned, to produce a higher-resolution output. **Figure 8.22** illustrates the basic pipelined structure.

Since each stage is typically a low-resolution flash converter, pipelined converters are capable of quite high resolution — up to 16 bits — and sample rates in the hundreds of Msps, even into the Gsps (gigasamples per second) range. There is a delay before the first sample emerges, of course, since an N-stage pipeline converter must perform N conver-

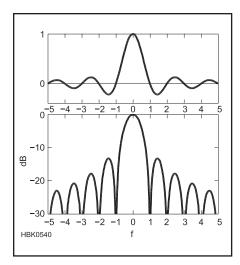

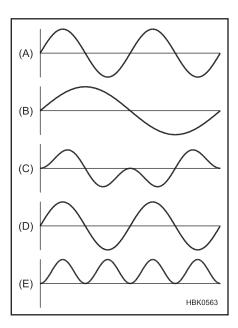

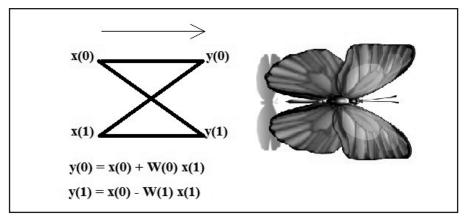

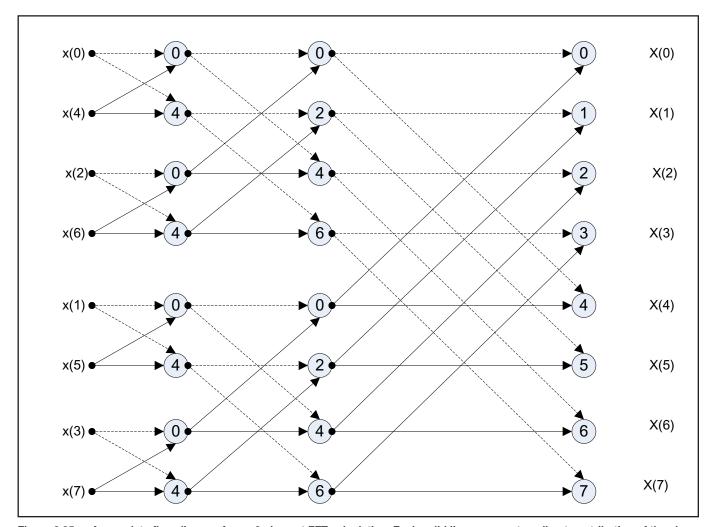

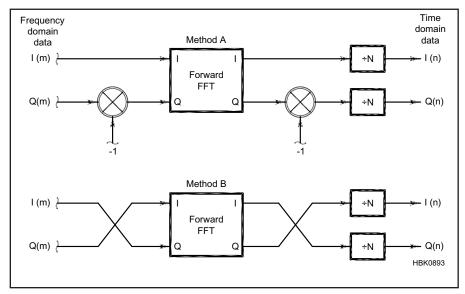

Figure 8.24 — Signal-to-noise ratio due to aperture jitter. [from Figure 1 of Analog Devices Application Note AN-501, available at www.analog.com, used with permission]